# User's Manual of the Microphone Array Mark III version 2

**ROCHET Cedrick**

Information Access Division National Institute of Standards and Technology

> Interactive Systems Labs Universität Karlsruhe

> > September 14, 2005

## Contents

| 1 | Intr                                                                                                   | oduction                                                                                                                                                                                                                                                                                                                                                            | 3                                                   |

|---|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|   | 1.1                                                                                                    | Features Summary                                                                                                                                                                                                                                                                                                                                                    | 3                                                   |

|   | 1.2                                                                                                    | Motherboard Layout                                                                                                                                                                                                                                                                                                                                                  | 4                                                   |

|   | 1.3                                                                                                    | Microboard Layout                                                                                                                                                                                                                                                                                                                                                   | 5                                                   |

|   | 1.4                                                                                                    | Powerboard Layout                                                                                                                                                                                                                                                                                                                                                   | 5                                                   |

|   | 1.5                                                                                                    | Block Diagram                                                                                                                                                                                                                                                                                                                                                       | 6                                                   |

|   | 1.6                                                                                                    | Minimum requirement                                                                                                                                                                                                                                                                                                                                                 | 6                                                   |

| 2 | Har                                                                                                    | dware Installation Process                                                                                                                                                                                                                                                                                                                                          | 7                                                   |

| 3 | Soft                                                                                                   | ware Installation Process                                                                                                                                                                                                                                                                                                                                           | 8                                                   |

|   | 3.1                                                                                                    | BOOTP server                                                                                                                                                                                                                                                                                                                                                        | 8                                                   |

|   | 3.2                                                                                                    | Kernel tuning                                                                                                                                                                                                                                                                                                                                                       | 10                                                  |

| 4 | Test                                                                                                   | ing the setup                                                                                                                                                                                                                                                                                                                                                       | 11                                                  |

|   | 4.1                                                                                                    | The oscilloscope                                                                                                                                                                                                                                                                                                                                                    | 11                                                  |

| 5 | Mal                                                                                                    | king the first capture                                                                                                                                                                                                                                                                                                                                              | 13                                                  |

| 6 | Adv                                                                                                    | anced Features                                                                                                                                                                                                                                                                                                                                                      | 14                                                  |

|   |                                                                                                        | Microphone array Status IEDa                                                                                                                                                                                                                                                                                                                                        |                                                     |

|   | 6.1                                                                                                    | Microphone array Status LEDs                                                                                                                                                                                                                                                                                                                                        | 15                                                  |

|   | 6.1<br>6.2                                                                                             | Multiple microphone arrays Synchronization                                                                                                                                                                                                                                                                                                                          | 15<br>15                                            |

| 7 | 6.2                                                                                                    | 1 5                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| 7 | 6.2                                                                                                    | Multiple microphone arrays Synchronization                                                                                                                                                                                                                                                                                                                          | 15                                                  |

| 7 | 6.2<br><b>Trou</b>                                                                                     | Multiple microphone arrays Synchronization                                                                                                                                                                                                                                                                                                                          | 15<br><b>17</b><br>17                               |

| 7 | 6.2<br><b>Trou</b><br>7.1                                                                              | Multiple microphone arrays Synchronization <b>ibleshooting</b> Dhcpd error message at startup         The packets arrives to the Mark III but the IP OK LED         doesn't light                                                                                                                                                                                   | 15<br><b>17</b>                                     |

| 7 | 6.2<br><b>Trou</b><br>7.1                                                                              | Multiple microphone arrays Synchronization                                                                                                                                                                                                                                                                                                                          | 15<br><b>17</b><br>17<br>17                         |

| 7 | 6.2<br><b>Trou</b><br>7.1<br>7.2                                                                       | Multiple microphone arrays Synchronization                                                                                                                                                                                                                                                                                                                          | 15<br><b>17</b><br>17<br>17<br>18                   |

| 7 | <ul> <li>6.2</li> <li>Trou</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ul>              | Multiple microphone arrays Synchronization <b>ibleshooting</b> Dhcpd error message at startup         The packets arrives to the Mark III but the IP OK LED         doesn't light         The amplification seems to double between the 22K mode         and 44K mode         Do I have the latest PROM version?                                                    | 15<br><b>17</b><br>17<br>17<br>17<br>18<br>18       |

| 7 | <ul> <li>6.2</li> <li>Trou</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ul> | Multiple microphone arrays Synchronization <b>ibleshooting</b> Dhcpd error message at startup         The packets arrives to the Mark III but the IP OK LED         doesn't light         The amplification seems to double between the 22K mode         and 44K mode         Do I have the latest PROM version?         How do I know if the array is in 22K mode? | 15<br><b>17</b><br>17<br>17<br>17<br>18<br>18<br>18 |

| 7 | <ul> <li>6.2</li> <li>Trou</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ul>              | Multiple microphone arrays Synchronization <b>ibleshooting</b> Dhcpd error message at startup         The packets arrives to the Mark III but the IP OK LED         doesn't light         The amplification seems to double between the 22K mode         and 44K mode         Do I have the latest PROM version?                                                    | 15<br><b>17</b><br>17<br>17<br>17<br>18<br>18       |

## 1 Introduction

## 1.1 Features Summary

| Form Factor                | * | Motherboard 121mm x 139mm, 4 layers PCB.  |

|----------------------------|---|-------------------------------------------|

|                            | * | Daughterboard 80mm x 159mm, 4 layers PCB. |

|                            | * | Powerboard 49mm x 72mm, 1 layer PCB       |

| Processing Unit            | * | Xilinx FPGA Spartan 2 XC2S200             |

| PROM                       | * | Prom Xilinx 17S200APC                     |

| Memory                     | * | 4x 4Mbits SRAM                            |

| On-Board LAN               |   | Fast Ethernet Link LSI (L80225)           |

|                            | * | 1 RJ45 Port                               |

|                            | * | 1 MAC DIP                                 |

| Power Connector            | * | 3.5mm Jack Connector                      |

| Daughterboard Connectors   | * | 8x 16 Pins Connector                      |

| Synchronization Connectors | * | Slave Synchronization OUT                 |

|                            | * | Slave Synchronization IN                  |

|                            | * | Master Synchronization OUT                |

| Additional Connectors      | * | ON/OFF connector                          |

|                            | * | Reset connector                           |

|                            | * | Capture connector                         |

|                            | * | Batteries board supply connector          |

|                            |   |                                           |

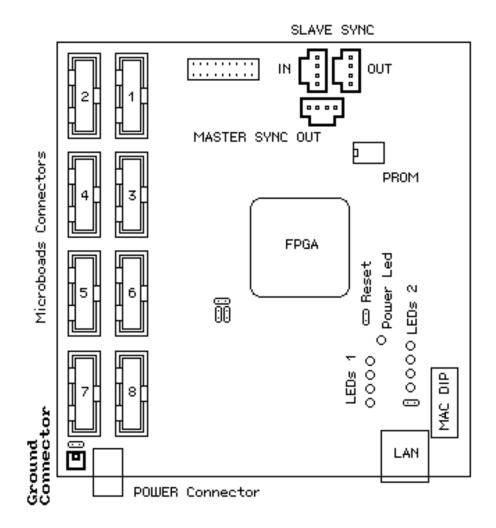

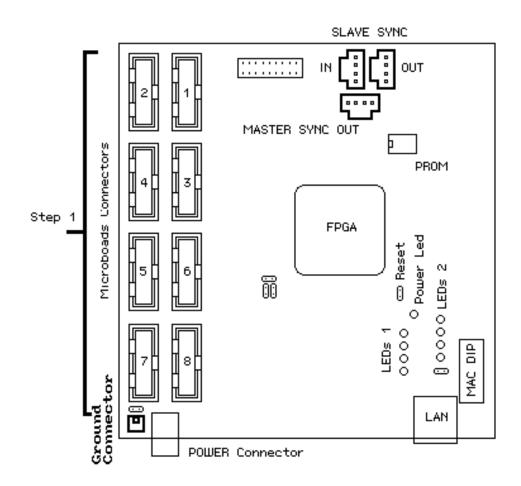

## 1.2 Motherboard Layout

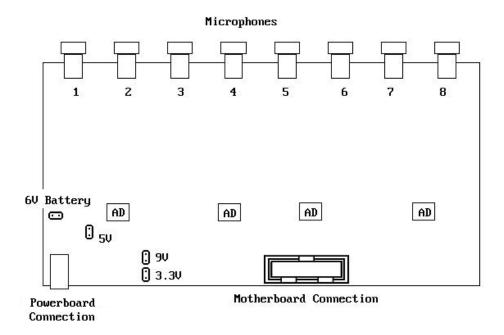

## 1.3 Microboard Layout

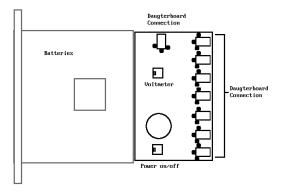

## 1.4 Powerboard Layout

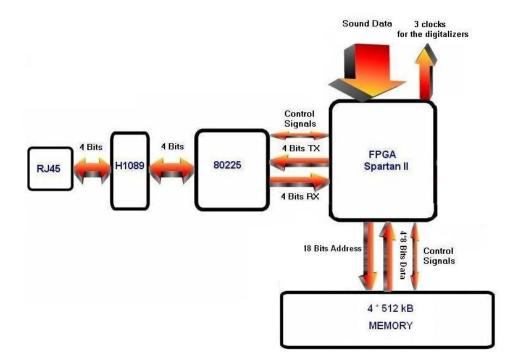

## 1.5 Block Diagram

## 1.6 Minimum requirement

| Computer:   | * | 1Ghz CPU                     |

|-------------|---|------------------------------|

|             | * | 512 Mbytes memory            |

|             | * | 1 Fast ethernet network card |

| <b>C</b> () | * | I: 04                        |

| Software:   | ~ | Linux 2.4                    |

|             | * | gcc 3.3                      |

|             | * | Smartspace CVS file          |

#### 2 Hardware Installation Process

To setup the microphone array, you must complete the following steps:

- Step 1 Plug the 8 data cables between the Motherboard and the 8 Microboards IN THE ORDER described on the figure below.

- Step 2 Plug the 8 power cables between the Microboard and the Powerboard.

- Step 3 Plug the voltmeter on the powerboard on the connector ME-TER. Put 4 AAs battery in the battery chamber.

- Step 4 Plug the switch connector on the connector POWER. TURN IT ON only when capturing data.

- Step 5 Plug the ground cable between the motherbard GROUND connector and the box shielding if you are using a metal box otherwise don't plug it.

- Step 6 Plug the power and Ethernet cables on the Motherboard.

Congratulations you have accomplished the hardware installation ! Turn on the power or connect the power cable to the power outlet. Continue with the software installation.

#### **3** Software Installation Process

#### 3.1 BOOTP server

Just after being power up, the microphone array is doing a BOOTP request on the network. You need on a computer, in direct liaison or connected through a switch, a DHCP daemon.

The DHCP protocol allows a host which is unknown to the network administrator to be automatically assigned a new IP address out of a pool of IP addresses for its network. In order for this to work, the network administrator allocates address pools in each subnet and enters them into the *letcldhcpd.conf* file. On startup, dhcpd reads that file and stores a list of available addresses on each subnet in memory.

(a) Step 01

(b) Step 02

(c) Step 03

(d) Step 04

(e) Step 05

(f) Step 06

First, you need to create the file as administrator on the machine *letcldhcpd.conf* Here is a copy of the file *dhcpd.conf*

```

option subnet-mask 255.255.255.0;

option broadcast-address 10.0.0.255;

option routers 10.0.0.1;

option domain-name-servers 10.0.0.1;

option domain-name "array.org";

ddns-update-style ad-hoc;

subnet 10.0.0.0 netmask 255.255.255.0 {

host array2 {

hardware ethernet 10:00:00:00:03:00;

fixed-address 10.0.0.2;

}

host array3 {

hardware ethernet 10:00:00:00:03:CA;

fixed-address 10.0.0.3;

}

host array4 {

hardware ethernet 10:00:00:00:03:FF;

fixed-address 10.0.0.4;

}

}

```

In order to activate the daemon you have to enter the following command:

> dhcpd

Now the green LED closest to the SRAM memory should light.

#### 3.2 Kernel tuning

toto

The amount of data created by the microphone array system is about 4.4MBytes a second if the frequency doubler is not activated otherwise, it goes up to 10 MBytes a second. To solve the possible packet loss problem, you have two ways:

- tune the Linux kernel,

- or upgrade the machine.

#### Tune the Linux kernel

Sysctl.conf is a simple file containing sysctl values to be read in and set by sysctl. Sysctl is used to modify kernel parameters at runtime. The parameters available are those listed under /proc/sys/ Here is a copy of the file in:*letclsysctl.conf*

```

# Kernel sysctl configuration file for Red Hat Linux

# For binary values, 0 is disabled, 1 is enabled. See sysctl(8) and

# sysctl.conf(5) for more details.

# Controls IP packet forwarding

net.ipv4.ip_forward = 0

# Controls source route verification

net.ipv4.conf.default.rp filter = 1

# Controls the System Request debugging functionality of the kernel

kernel.sysrq = 1

# Controls whether core dumps will append the PID to the core filename.

# Useful for debugging multi-threaded applications.

kernel.core_uses_pid = 1

#increase linux TCP bufferlimits

net.core.rmem_max = 8388608

net.core.wmem_max = 8388608

net.core.rmem_default = 2097152

net.core.wmem_default = 2097152

#increase linux autotuning TCP buffer limits

net.ipv4.tcp_rmem = 4096 2097152 8388608

net.ipv4.tcp_wmem = 4096 2097152 8388608

net.ipv4.tcp_mem = 8388608 8388608 8388608

```

First you have to be logged as administrator on the machine. After changing your *letclsysctl.conf* you need to apply the settings. To do so, you have to enter the following command:

> sysctl -p

#### 4 Testing the setup

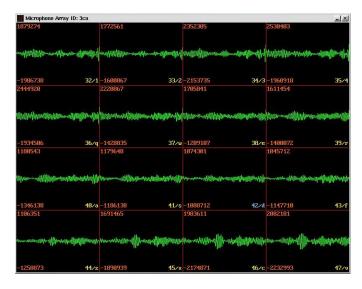

The best way to test the setup of the Mark III microphone array is to use the software called oscilloscope. You will be able **TO SEE EACH CHANNEL** of the microphone array and **TO TEST THE ORDER** of the boards.

#### 4.1 The oscilloscope

The oscilloscope was made with the goal of viewing, listening and recording in a file the data received from one channel. It can be found directly on

the web page: http://www.nist.gov/smartspace/cmaiii.html or in the cvs archive on the same page.

Figure 1: Oscilloscope in listening mode of the channel 42.

At the top of the window, the ID of the microphone array is given and the PROM version. In our case it's 3ca.

The red numbers represents the highest and the lowest points of the channel at the time of picture.

The yellow numbers and letters represent the channel number/the key. For example in the top left corner is the channel 32 and if you type 1 you will listen it or the bottom right corner is the channel 47 and if you type 'v' you will listen to it.

The figure 2 represents the oscilloscope in record mode of the channel 21 at the UNIX time 1048627720 in the file /tmp/21-1048627720.ary.

The figure 2 represents also different channels (16 to 31) than the previous one (32 to 47). To pass from on quarter of 64 to another you have to use the keys F1, F2, F3, F4, F5:

- F1: first quarter with the channels from 0 to 15,

- F2: second quarter with the channels from 16 to 31,

- F3: third quarter with the channels from 32 to 47,

- F4: fourth quarter with the channels from 48 to 63,

| 2030667<br>796979 | 16/1 -2170880<br>2483049<br>/tmp/21-1048 | 17/2 -2360757<br>2281523 | 18/3 -2302216<br>2117438 | 19   |

|-------------------|------------------------------------------|--------------------------|--------------------------|------|

| MMM               |                                          | MMM MMM                  | mm mm                    | www. |

| 2550600<br>356106 | 20∕q -3449260<br>2895361                 | 21/u -3111769<br>2937588 | 22∕e -2781017<br>3490326 | 23   |

| MMM               | mmmmmm.                                  | mmmmm                    | nmmmml.                  | NWW  |

|                   |                                          | 25/s -2672332            | 26/d -3193715            | 2    |

Figure 2: Oscilloscope in capturing mode of the channel 21.

• F5: all quarters.

If you try F5 you might not be able to see of the channels because the window is in 1600\*1200. So another key that might be interesting is the tab key. It toggles from window to full screen the oscilloscope.

To get a capture of a channel you have first to select it with the corresponding key in our case w and then press [space] to toggle the capture in the file on/off.

#### 5 Making the first capture

First you should download the latest version of the smartflow. You will find it on the webpage: http://www.nist.gov/smartspace/nsfs.html

Then you should compile it and go to Audio/AudioCapture/sources/mk3cap.In this directory you will find compiled different executables. I recommend to use the mk3cap\_100f\_44K where 100f represents the number of samples sent in one block to the next client in smartflow and 44K the sampling frequency. The options for the software are given by: >  $mk3cap_100f_44K -h$

So for example: >  $mk3cap_100f_44K - d10.0.0.2 - t20/tmp/test.ary$

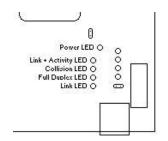

| Power LED       | Indicate if power is ON or OFF.                |

|-----------------|------------------------------------------------|

|                 | 0 = OFF                                        |

|                 | 1 = ON                                         |

| Link+Activity   | Indicate Link or Activity on the Ethernet.     |

| LED             | 0 = Link Detect                                |

|                 | Blink = Link Detect and Activity               |

|                 | 1 = No Link Detect                             |

| Collision LED   | Indicate Collision on the Ethernet.            |

|                 | 0 = Collision Detect                           |

|                 | 1 = No Collision                               |

| Full Duplex LED | Indicate the Duplex Mode on the Ethernet.      |

|                 | 0 = Full Duplex Mode Detect with Link Pass     |

|                 | 1 = Half Duplex                                |

| Link LED        | Indicate a 10/100 Mbps Detect on the Ethernet. |

|                 | 0 = 100Mbit Mode Detected with Link Pass       |

|                 | 1 = 10Mbit Mode Detected                       |

This will record 10 sec of data in the file /tmp/test.ary at 44Khz with the microphone array at the address 10.0.0.2.

## 6 Advanced Features

Figure 3: Network Status LEDs

#### 6.1 Microphone array Status LEDs

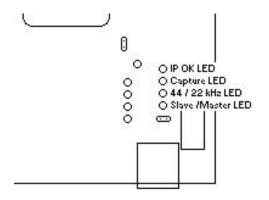

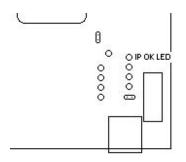

Figure 4: Microphone array Status LEDs

#### 6.2 Multiple microphone arrays Synchronization

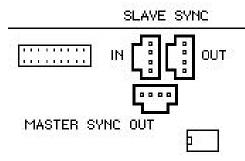

Figure 5: Microphone arrays Synchronization connectors

With the cable provided the synchronization is possible with a least 4 Motherboards in daisy chain. To do with even more Motherboards, you might have to upgrade the cable to an other one of better quality.

The delay introduce between two synchronized boards is about 3 ns  $(3*10^{-9}s)$ . The delay is the time needed to propagate along the about 30cm of the cable. Compared to the frequency of 22050Hz of the converter the error is about 0.007%.

| Name            | Description                                             |  |  |  |

|-----------------|---------------------------------------------------------|--|--|--|

| IP OK LED       | Indicate if the Microphone Array Mark III has an IP ad- |  |  |  |

|                 | dress Ethernet.                                         |  |  |  |

|                 | 0 = No IP address and waiting an BOOTP reply            |  |  |  |

|                 | 1 = Has an IP address                                   |  |  |  |

| Capture LED     | Indicate if the Microphone Array Mark III is capturing  |  |  |  |

|                 | sound.                                                  |  |  |  |

|                 | 0 = No capture                                          |  |  |  |

|                 | 1 = Capturing                                           |  |  |  |

| 44 / 22 kHz LED | Indicate if the Microphone Array Mark III is capturing  |  |  |  |

|                 | at a frequency of 44100Hz or 22050Hz.                   |  |  |  |

|                 | 0 = 22050Hz mode                                        |  |  |  |

|                 | 1 = 44100Hz mode                                        |  |  |  |

| Slave / Master  | Indicate if the Microphone Array Mark III is in slave   |  |  |  |

| LED             | mode.                                                   |  |  |  |

|                 | 0 = Master mode                                         |  |  |  |

|                 | 1 = Slave mode                                          |  |  |  |

| Name            | Description                                            |  |  |  |  |  |

|-----------------|--------------------------------------------------------|--|--|--|--|--|

| Master Synchro- | Connector for the synchronization cable. The other     |  |  |  |  |  |

| nization OUT    | end of the synchronization cable should be connected   |  |  |  |  |  |

|                 | to Slave Synchronization IN. The synchronization sig-  |  |  |  |  |  |

|                 | nals are going out of the Motherboard , in Master Moc  |  |  |  |  |  |

|                 | through this connector                                 |  |  |  |  |  |

| Slave Synchro-  | Connector for the synchronization cable. The other end |  |  |  |  |  |

| nization IN     | of the synchronization cable should be connected to    |  |  |  |  |  |

|                 | Slave Synchronization OUT or Master Synchronization    |  |  |  |  |  |

|                 | OUT. The synchronization signals are going in the Moth |  |  |  |  |  |

|                 | erboard, in Slave Mode (to be detected), through this  |  |  |  |  |  |

|                 | connector                                              |  |  |  |  |  |

| Slave Synchro-  | Connector for the synchronization cable. The other end |  |  |  |  |  |

| nization OUT    | of the synchronization cable should be connected to    |  |  |  |  |  |

|                 | Slave Synchronization IN. The synchronization signals  |  |  |  |  |  |

|                 | are propagate from the Slave Synchronization IN to an- |  |  |  |  |  |

|                 | other Motherboard through this connector               |  |  |  |  |  |

#### 7 Troubleshooting

#### 7.1 Dhcpd error message at startup

Look at the documentation of dhcpd

7.2 The packets arrives to the Mark III but the IP OK LED doesn't light

The problem is that the *letcldhcpd.conf* and the hardware Ethernet (MAC) addresse on the Mark III microphone array are not the same.

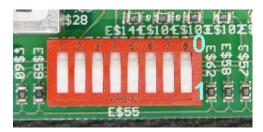

Figure 6: The MAC dip.

| Fixed by the onboard program                 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|----------------------------------------------|---|---|---|---|---|---|---|---|

| 0001 0000 0000 0000 0000 0000 0000 0000 0000 | x | x | x | x | x | x | x | x |

The RED DIP switch (cf figure 6)setups the MAC address. A MAC address is made of 48 bits. The DIP switch fixed the last 8 ones and the onboard program fixed the 40 remaining one. By default, as one the photo, the MAC address is : 10:00:00:00:03:00.

Examples:

- If the switch 1 on the DIP is changed, compared to the photo, the MAC address becomes : 10:00:00:00:03:80.

- If the switch 8 on the DIP is changed, compared to the photo, the MAC address becomes : 10:00:00:00:03:01.

- If all the switches on the DIP are changed, compared to the photo, the MAC address becomes : 10:00:00:00:03:FF.

## 7.3 The amplification seems to double between the 22K mode and 44K mode

It's true the amplification double but unfortunalty this comes from the digitalizer itself so nothing can be done about it.

#### 7.4 Do I have the latest PROM version?

To know that, you have to start the digital oscilloscope and see the information at the top. it shoould be written something like: "Microphone Array ID: 300 with PROM CMA3v920". The value that you are looking for is CMA3v920. At this date that's the latest verion but check the website for updates

#### 7.5 How do I know if the array is in 22K mode?

Check the LED on the Motherboard (cf figure 4)

#### 7.6 How do I know if the array is in slave mode?

Check the LED on the Motherboard (cf figure 4)

#### 7.7 What is the default voltage of the Motherboard?

The default voltage is 9V.