### CHIPS AI/AE for Rapid, Industry-informed Sustainable Semiconductor Materials and Processes (CARISSMA) Competition Executive Summary

| Federal Agency Name:                                                 | U.S. Department of Commerce (DOC), National Institute of Standards and Technology (NIST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Federal Funding Opportunity<br>Title:                                | FY 2025 CHIPS AI/AE for Rapid, Industry-informed<br>Sustainable Semiconductor Materials and Processes<br>(CARISSMA) Competition Notice of Funding<br>Opportunity (NOFO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Funding Opportunity Number:                                          | 2025-NIST-CHIPS-AIAE-Sustainability-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Funding Opportunity<br>Description:                                  | Subject to the availability of funds, this NOFO seeks<br>applications for industry-informed, university-based<br>artificial intelligence-powered autonomous<br>experimentation (AI/AE) collaborations, including<br>research and development, education and workforce<br>development, and related activities relevant to<br>sustainable semiconductor materials and processes. If<br>successful, awards made under this NOFO will support<br>the long-term viability of next-generation domestic<br>semiconductor manufacturing, accelerating the<br>discovery, design, synthesis, and adoption of materials<br>and processes, and the development of new<br>researchers needed to meet the industry's technology,<br>economic, and sustainability goals. |

| Announcement Type:                                                   | Initial.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Funding Instrument Type:                                             | Awards under this program will be made as other transaction agreements as authorized, in 15 U.S.C. § 4659(a)(1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Assistance Listing Number<br>(formerly known as the CFDA<br>Number): | 11.042: CHIPS R&D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Award Period of Performance:                                         | Project period of performance up to five (5) years.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Goals and Objectives:

Through awards made under this NOFO, the CHIPS Research and Development Office (CHIPS R&D) aims to achieve the following objectives:

- 1) Accelerate research into and delivery of targeted, industry-relevant, sustainable semiconductor materials and processes through the application of AI/AE;

- 2) Propagate models for incorporating sustainability metrics into semiconductor industry materials design and discovery, in addition to continued advancement in power, performance, area, cost, or other relevant technology metrics;

- 3) Expand the capabilities of emerging research institutions and other emerging R&D participants through cohesive, innovative teams of universities, industry, government labs, and other stakeholders; and

- 4) Build an exceptional workforce of university graduates and faculty with AI/AE R&D expertise.

If successful, CHIPS R&D investments under this NOFO should demonstrate that new sustainable semiconductor materials and processes, meeting industry needs, can be designed and adopted for industry testing within five years. Further, the investment should accelerate a step-change in the number of universities, researchers, and graduates participating in the U.S. semiconductor R&D ecosystem.

Under this NOFO, eligible applicants are domestic Subrecipients: accredited institutions of higher education and domestic non-profit or for-profit organizations that manage consortia of accredited institutions of higher education. A domestic entity is one that is incorporated within the United States (including a U.S. territory) with its principal place of business in the United States (including a U.S. territory). Eligible applicants may submit only one concept paper and, if invited, one full application.

> Eligible subrecipients under this NOFO include accredited institutions of higher education; for-profit organizations or non-profit organizations; State, local, territorial, and Tribal governments; Federally Funded Research and Development Centers; Federal entities; foreign partners; and other entities eligible to participate

# Eligible Applicants and

|                             | as applicants. Eligible subre multiple applications.                                                                                                                                                                                                     | cipients may participate in                                                                                                                                                    |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                             | Vendors selling goods or se<br>course of business are not o<br>under this NOFO.                                                                                                                                                                          |                                                                                                                                                                                |  |

| Available Funding:          | CHIPS R&D anticipates that the total Federal funds available under this NOFO to be approximately \$100 million.                                                                                                                                          |                                                                                                                                                                                |  |

| Cost Share or Match:        | Non-federal cost share is not<br>However, CHIPS R&D enco<br>in their applications opportu<br>investment, which may inclu<br>expertise, intellectual proper<br>forms of partner co-investme<br>of performance. For more in<br>investments, see Section 3. | ourages applicants to detail<br>nities for optional co-<br>ide industry-provided<br>rty, facility access, or other<br>ent during the award period<br>formation on optional co- |  |

| Estimated Number of Awards: | Multiple awards in amounts ranging from approximately<br>\$20 to \$40 million per award in Federal funds, with a<br>period of performance of up to five (5) years, per award<br>are anticipated under this NOFO, for projects varying in<br>scope.       |                                                                                                                                                                                |  |

| Submission Dates and Times: | Relevant dates in the application process for this NOFO are listed below in Table 1 and described in the text that follows.                                                                                                                              |                                                                                                                                                                                |  |

|                             | Table 1. Key Dates for 20<br>Sustainability-01                                                                                                                                                                                                           | 025-NIST-CHIPS-AIAE-                                                                                                                                                           |  |

|                             | NOFO Publication Date                                                                                                                                                                                                                                    | October 30, 2024                                                                                                                                                               |  |

|                             | Informational Webinar                                                                                                                                                                                                                                    | November 8, 2024                                                                                                                                                               |  |

|                             | Proposers' Day<br>Meeting                                                                                                                                                                                                                                | November 15, 2024                                                                                                                                                              |  |

|                             | Concept Papers Due                                                                                                                                                                                                                                       | January 13, 2025, 11:59<br>PM, 75 days after<br>publication                                                                                                                    |  |

|                             | Invited Full<br>Applications Due                                                                                                                                                                                                                         | Full application deadlines<br>will be communicated to<br>invited applicants at the<br>time of invitation                                                                       |  |

The U.S. Department of Commerce may amend this NOFO at any time. It may also close this funding opportunity with at least 60 days' notice. Any changes will be communicated via https://www.grants.gov and https://www.chips.gov. Concept papers and full applications must be submitted electronically through Grants.gov. Paper or emailed How to Apply: submissions will not be accepted. Prospective applicants and subrecipients are required to have an active registration in the System of Award Management (https://sam.gov/content/home) prior to submitting an application and throughout the award term and are encouraged to begin the process of registering as early as possible. Informational Webinar: Informational Webinar: The National Institute of Standards and Technology (NIST) CHIPS for America Research and Development Office (CHIPS R&D) will host an informational webinar on November 8, 2024, to provide general information regarding this NOFO, offer general guidance on preparing applications, and answer questions. Proprietary technical discussions about specific project ideas will not be permitted during the webinar, and CHIPS R&D staff will not critique or provide feedback on any specific project ideas while they are being developed by an applicant, brought forth during the webinar, or at any time before the deadline for applications. However, questions about this funding opportunity, eligibility requirements, evaluation and award criteria, selection process, and the general characteristics of a competitive application will be addressed during the webinar and by e-mail for inquiries sent to research@chips.gov with "2025-NIST-CHIPS-AIAE-Sustainability-01 Questions" in the subject line. There is no cost to attend the webinar, but participants must register in advance. Participation in the webinar is not required and will not be considered in the review and selection process described in Section 5.5 of this NOFO.

**Proposers' Day and Teaming Meetings:** In addition to the informational webinar described above, CHIPS R&D plans to host one or more Proposers' Days to promote awareness of the funding opportunity and

|                                         | provide a forum for organizations to identify prospective<br>partners. Information about the event can be found on<br>the CHIPS for America <u>events website</u> .                                                                                                                                                                                                                                                                         |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application Submission<br>Requirements: | <b>Concept Papers:</b> The submission of a concept paper<br>is required. Concept papers will be accepted only<br>through Grants.gov. Concept papers must be received<br>at Grants.gov no later than 11:59 p.m. Eastern Time, on<br>January 13, 2025. Concept papers received after the<br>specified deadline will not be reviewed or considered.                                                                                            |

|                                         | Applicants should be aware, and factor into their<br>concept paper submission planning, that the Grants.gov<br>system closes periodically for routine maintenance.<br>Applicants should visit Grants.gov for information on<br>any scheduled closures. Please note that an active<br>registration in the <u>System for Award Management</u> is<br>required to submit concept paper materials through<br>Grants.gov.                         |

|                                         | <b>Full Applications:</b> Full applications will be accepted<br>only from those applicants that are invited after<br>completion of the concept paper evaluation. Full<br>applications will be accepted only through Grants.gov.<br>The full application deadline will be communicated to<br>invited applicants at the time of invitation. Full<br>applications received after the specified deadline will<br>not be reviewed or considered. |

| Agency Contacts:                        | Any inquiries regarding this NOFO must be submitted<br>to the agency points of contact listed in Section 7 of this<br>NOFO. Applicants may submit questions by e-mail to<br>the appropriate agency point of contact with "2025-<br>NIST-CHIPS-AIAE-Sustainability-01" in the subject line.                                                                                                                                                  |

|                                         | Programmatic and Technical Questions:                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                         | Research@chips.gov<br>Agreements Rules and Regulations:                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         | Lisa Ko<br><u>NOFO@nist.gov</u>                                                                                                                                                                                                                                                                                                                                                                                                             |

| Additional Information:                 | CHIPS R&D has a <u>public website</u> that includes a <u>Frequently Asked Questions</u> page and other information pertaining to this funding opportunity.                                                                                                                                                                                                                                                                                  |

# **Table of Contents**

| 1 | PROGRAM DESCRIPTION |                                                             |    |  |

|---|---------------------|-------------------------------------------------------------|----|--|

|   | 1.1 Progr           | ram Overview                                                | 10 |  |

|   | 1.1.1               | CHIPS R&D Mission and Goals                                 |    |  |

|   | 1.1.2               | NOFO Objectives                                             | 11 |  |

|   | 1.2 Defir           | nitions                                                     | 12 |  |

|   | 1.3 Back            | ground                                                      |    |  |

|   | 1.3.1               | Challenge: Economic Pressure                                | 14 |  |

|   | 1.3.2               | Challenge: Materials Co-optimization and Time to Deployment |    |  |

|   | 1.3.3               | Challenge: Limited Research Workforce                       |    |  |

|   | 1.3.4               | Opportunity: AI/AE                                          | 16 |  |

|   | 1.3.5               | Opportunity: Emerging Research Institutions                 | 16 |  |

|   | 1.4 Fund            | ing Opportunity Detailed Description                        | 17 |  |

|   | 1.4.1               | Operational Areas                                           | 17 |  |

|   | 1.4.2               | Materials Classes and Applications                          |    |  |

|   | 1.4.3               | Co-optimization Targets                                     |    |  |

|   | 1.4.4               | Programmatic Targets                                        |    |  |

|   | 1.4.5               | Phases of Work and SMART Milestones                         |    |  |

|   | 1.4.6               | Project Team Capabilities and Structure                     |    |  |

|   | 1.5 OA-S            | Specific Activities and Deliverables                        |    |  |

|   | 1.5.1               | OA1: Convening, Roadmapping, and Technology Transfer        |    |  |

|   | 1.5.2               | OA2: AI/AE Infrastructure and Research                      |    |  |

|   | 1.5.3               | OA3: Education and Workforce Development                    |    |  |

|   | 1.6 Gene            | ral Roles of the Award Recipient and NIST                   |    |  |

|   | 1.6.1               | Substantial Involvement of CHIPS R&D                        |    |  |

|   | 1.6.2               | Responsibilities of Recipient                               |    |  |

|   | 1.6.3               | Involvement of NIST and CHIPS R&D                           |    |  |

|   | 1.6.4               | Joint Activities Between Recipient and NIST and CHIPS R&D   |    |  |

|   | 1.6.5               | Coordination with other Federal R&D Programs                |    |  |

|   | 1.7 Broad           | der Impacts                                                 |    |  |

|   | 1.7.1               | Commitments to Future Investment                            |    |  |

|   | 1.7.2               | Creating Inclusive Opportunities                            |    |  |

|   | 1.7.3               | Environmental Responsibility                                |    |  |

|   | 1   | .7.4    | Community Impact and Support                                               | 33 |

|---|-----|---------|----------------------------------------------------------------------------|----|

|   | 1.8 | Gover   | rnment-Furnished Property (GFP) and Government Furnished Information (GFI) | 34 |

| 2 | F   | FEDERA  | AL AWARD INFORMATION                                                       | 34 |

|   | 2.1 | Fundi   | ng Availability                                                            | 34 |

|   | 2   | .1.1    | Funding Instrument and Payments                                            | 34 |

|   | 2   | .1.2    | Multi-Year Funding Policy                                                  | 34 |

|   | 2.2 | Eligib  | le Uses of Funds                                                           | 34 |

|   | 2   | .2.1    | Construction                                                               | 35 |

|   | 2   | .2.2    | Indirect (F&A) Costs                                                       | 35 |

|   | 2.3 | Public  | c Access to CHIPS R&D Research                                             | 36 |

|   | 2.4 | Funda   | mental Research                                                            | 36 |

|   | 2   | .4.1    | Fundamental Research Declaration                                           | 36 |

|   | 2   | .4.2    | On-Campus Research                                                         | 36 |

|   | 2   | .4.3    | Pre-Publication Reviews                                                    | 37 |

|   | 2.5 | Resea   | rch Security                                                               | 37 |

|   | 2   | .5.1    | Research Security Definitions                                              | 37 |

|   | 2   | .5.2    | Authorities                                                                | 37 |

|   | 2   | .5.3    | Requirement for a Research Security Plan or Program                        | 38 |

|   | 2   | .5.4    | Covered Individuals                                                        | 39 |

|   | 2   | .5.5    | Foreign Entities of Concern                                                | 40 |

|   | 2   | .5.6    | Research Security Review and Risk Determination                            | 40 |

|   | 2   | .5.7    | Non-Discrimination Policy                                                  | 41 |

|   | 2   | .5.8    | Potential for Mitigation                                                   | 41 |

|   | 2   | .5.9    | Requirement for Recipients to Update Research Security-Related Information | 41 |

|   | 2.6 | Intelle | ectual Property (IP) and Domestic Production                               | 42 |

|   | 2   | .6.1    | Intellectual Property                                                      | 42 |

|   | 2   | .6.2    | Domestic Production                                                        | 42 |

|   | 2   | .6.3    | Domestic Control                                                           | 43 |

|   | 2   | .6.4    | Commercial Viability and Domestic Production Plan (CVDP)                   | 44 |

| 3 | E   | ELIGIBI | LITY INFORMATION                                                           | 45 |

|   | 3.1 | Eligib  | le Applicants and Subrecipients                                            | 45 |

|   | 3   | .1.1    | Federally Funded Research and Development Centers                          | 46 |

|   | 3   | .1.2    | Federal Entities                                                           | 47 |

|   | 3   | .1.3    | Individuals and Unincorporated Sole Proprietors                            | 47 |

|   | 3.   | 1.4    | Foreign Partners and Foreign Research Activities          | .47  |

|---|------|--------|-----------------------------------------------------------|------|

|   | 3.2  | Option | nal Co-investment                                         | .48  |

|   | 3.3  | Allow  | able Costs                                                | .49  |

| 4 | Al   | PPLIC  | ATION AND SUBMISSION INFORMATION                          | .49  |

|   | 4.1  | Overv  | iew                                                       | .49  |

|   | 4.2  | Where  | e to obtain an Application Package                        | .49  |

|   | 4.3  | Page ( | Count Guidance                                            | . 50 |

|   | 4.4  | Subm   | ission Format                                             | . 50 |

|   | 4.4  | 4.1    | Amendments                                                | . 50 |

|   | 4.4  | 4.2    | Proprietary and Sensitive Business Information            | . 50 |

|   | 4.5  | Conce  | pt Paper Instructions                                     | . 50 |

|   | 4.:  | 5.1    | Required Forms and Documents                              | .51  |

|   | 4.:  | 5.2    | Concept Paper Format and Guidelines                       | . 55 |

|   | 4.6  | Full A | pplication Instructions                                   | .56  |

|   | 4.0  | 6.1    | Required Forms and Documents                              | .56  |

|   | 4.0  | 6.2    | Attachment of Required Documents                          | .71  |

|   | 4.0  | 6.3    | Full Application Format and Guidelines                    | .72  |

|   | 4.7  | Appli  | cation Replacement Pages                                  | .74  |

|   | 4.8  | Uniqu  | e Entity Identifier and System for Award Management (SAM) | .74  |

|   | 4.9  | Subm   | ission Dates and Times                                    | .74  |

|   | 4.9  | 9.1    | Concept Papers                                            | .74  |

|   | 4.9  | 9.2    | Full Applications                                         | .75  |

|   | 4.10 | Interg | overnmental Review                                        | .75  |

|   | 4.11 | Fundi  | ng Restrictions                                           | .75  |

| 5 | Al   | PPLIC  | ATION REVIEW INFORMATION                                  | .75  |

|   | 5.1  | Conce  | pt Paper Evaluation Criteria                              | .75  |

|   | 5.   | 1.1    | Relevance to economic and national security               | .75  |

|   | 5.   | 1.2    | Overall Scientific and Technical Merit                    | .76  |

|   | 5.   | 1.3    | Project Management, Resources, and Budget                 | .76  |

|   | 5.   | 1.4    | Transition and Impact Strategy                            | .77  |

|   | 5.   | 1.5    | Education and Workforce Development (EWD)                 | .77  |

|   | 5.2  | Conce  | pt Paper Selection Factors                                | .77  |

|   | 5.3  | Full A | pplication Evaluation Criteria                            | .78  |

|   | 5.   | 3.1    | Relevance to Economic and National Security               | .78  |

| 5.3.2<br>5.3.3 |     | 3.2      | Overall Scientific and Technical Merit                      | .79  |

|----------------|-----|----------|-------------------------------------------------------------|------|

|                |     | 3.3      | Project Management, Resources, and Budget                   | . 79 |

|                | 5.  | 3.4      | Transition and Impact Strategy                              | . 80 |

|                | 5.  | 3.5      | Education and Workforce Development (EWD)                   | . 80 |

|                | 5.4 | Full A   | Application Selection Factors                               | . 81 |

|                | 5.5 | Revie    | w and Selection Process                                     | . 81 |

|                | 5.  | 5.1      | Initial Review of Applications                              | . 82 |

|                | 5.  | 5.2      | Review of Concept Papers                                    | . 82 |

|                | 5.  | 5.3      | Review of Full Applications                                 | . 83 |

|                | 5.6 | Addit    | ional Information                                           | . 86 |

|                | 5.  | 6.1      | Safety                                                      | . 86 |

|                | 5.  | 6.2      | Notification to Unsuccessful Applicants                     | . 86 |

|                | 5.  | 6.3      | Retention of Unsuccessful Applications                      | . 86 |

| 6              | Fe  | ederal A | Award Administration Information                            | . 86 |

|                | 6.1 | Federa   | al Award Notices                                            | . 86 |

|                | 6.2 | Admi     | nistrative and National Policy Requirements                 | . 86 |

|                | 6.  | 2.1      | Terms and Conditions                                        | . 86 |

|                | 6.  | 2.2      | Funding Availability and Limitation of Liability            | . 87 |

|                | 6.  | 2.3      | Collaborations with CHIPS R&D and Other Federal Agencies    | . 87 |

|                | 6.  | 2.4      | Use of Federal Government-Owned Intellectual Property       | . 88 |

|                | 6.  | 2.5      | Export Controls                                             | . 88 |

| 6.3 Reporting  |     | ting     | . 89                                                        |      |

|                | 6.  | 3.1      | Reporting Requirements                                      | . 89 |

|                | 6.  | 3.2      | Audit Requirements                                          | . 90 |

|                | 6.  | 3.3      | Federal Funding and Accountability Transparency Act of 2006 | . 90 |

| 7              | A   | GENC     | Y CONTACTS                                                  | .91  |

| 8              | O   | THER     | INFORMATION                                                 | .91  |

|                | 8.1 | Person   | nal and Business Information                                | .91  |

|                | 8.2 | Public   | e Website                                                   | .92  |

#### **Full Announcement Text**

## **1 PROGRAM DESCRIPTION**

The statutory authorities for the CHIPS AI/AE for Rapid, Industry-informed Sustainable Semiconductor Materials and Processes (CARISSMA) program NOFO are 15 U.S.C. § 4656(c) and 15 U.S.C. § 4659, as amended.<sup>a</sup>

# **1.1 PROGRAM OVERVIEW**

The 2022 CHIPS and Science Act appropriated \$50 billion to the U.S. Department of Commerce's (the Department or DOC) CHIPS for America program to strengthen semiconductor manufacturing in the United States. This amount includes \$39 billion for the Department to onshore semiconductor manufacturing through an incentives program and \$11 billion to advance U.S. leadership in semiconductor research and development (R&D). These R&D advances will primarily be realized through the following four programs: the CHIPS National Semiconductor Technology Center (NSTC), the CHIPS National Advanced Packaging Manufacturing Program (NAPMP), the CHIPS Metrology Program, and the CHIPS Manufacturing USA Program (MFG USA). These investments, across both the R&D and incentives programs, seek to strengthen U.S. competitiveness, support domestic production and innovation, create good jobs across the country—with working conditions consistent with the Good Jobs Principles published by the Department of Commerce and the U.S. Department of Labor—and advance U.S. economic and national security.

The CARISSMA program will complement these efforts by generating or enhancing sustainable semiconductor materials and processes. Research outputs should prove relevant and translatable to industry, the NSTC, the CHIPS Manufacturing USA Program, and other CHIPS programs. The competition should further enhance participation in and availability of academic-industry partnerships and research infrastructure for CHIPS Act funded activities and the development of a thriving semiconductor-related AI/AE talent pool.

#### 1.1.1 CHIPS R&D Mission and Goals

Within the CHIPS for America program, the mission of the National Institute of Standards and Technology (NIST) CHIPS Research and Development Office (CHIPS R&D) is to accelerate the development and commercial deployment of foundational semiconductor technologies by establishing, connecting, and providing access to domestic research efforts, tools, resources, workers, and facilities. CHIPS R&D aims to achieve the following goals by 2030:

• **U.S.** *Technology Leadership*: The United States improves its capacity to invent, develop, prototype, manufacture, and deploy the foundational semiconductor technologies of the future;

<sup>&</sup>lt;sup>a</sup> DOC CHIPS activities were authorized by Title XCIX—Creating Helpful Incentives to Produce Semiconductors for America of the William M. (Mac) Thornberry National Defense Authorization Act for Fiscal Year 2021 (Pub. L. 116-283), often referred to as the CHIPS Act, codified at 15 U.S.C. § 4651 et seq., as amended.

- *Accelerated Ideas to Market*: The best ideas achieve commercial scale as quickly and cost effectively as possible; and

- *Robust Semiconductor Workforce*: Inventors, designers, researchers, developers, engineers, technicians, and staff sustainably meet evolving domestic government and commercial sector needs.

# 1.1.2 NOFO Objectives

Accelerated discovery, design, and validation of new materials promises critical benefits to the future of the global semiconductor industry.<sup>b,c,d</sup> These materials must not only yield higher-performing semiconductor products but also address sustainability concerns challenging the industry, including the use of toxic chemicals, greenhouse gas (GHG) emissions, and water and energy efficiency. However, the deployment of new materials and processes can require years of research, development, testing, and validation.

AI/AE has emerged as a potentially game-changing approach to accelerate materials discovery and development. This NOFO therefore aims to create collaborations between academia and the private sector that are university-led, industry-informed, and relevant to sustainable semiconductor manufacturing. These collaborations should support the long-term viability of domestic semiconductor manufacturing by accelerating the discovery, design, synthesis, and deployment of new materials and processes; developing and connecting cutting-edge AI/AE techniques, know-how, and infrastructure; and developing new researchers needed to meet the industry's technological, economic, and sustainability goals.

If successful, CHIPS R&D investments under this NOFO should demonstrate that new sustainable semiconductor materials and processes, meeting industry needs, can be designed and adopted for industry testing within five years. Further, the investment should accelerate a step-change in the number of universities, researchers, and graduates participating in the U.S. semiconductor R&D ecosystem.

The resulting objectives under this NOFO are to:

- (1) Accelerate research into and delivery of targeted, industry-relevant, sustainable semiconductor materials and processes through the application of AI/AE;

- (2) Propagate models for incorporating sustainability metrics into semiconductor industry materials design and discovery, in addition to continued advancement in power, performance, area, cost, or other relevant technology metrics;

- (3) Expand the capabilities of emerging research institutions (ERIs) and other emerging R&D participants through cohesive innovative teams of universities, industry, government labs, and other stakeholders; and

<sup>&</sup>lt;sup>b</sup> Semiconductor Research Corporation, "MAPT Microelectronics and Advanced Packaging Technologies Roadmap", 2023. Available online at: <u>srcmapt.org/wp-content/uploads/2024/03/SRC-MAPT-Roadmap-2023-v4.pdf</u>

<sup>&</sup>lt;sup>c</sup> AI Aspirations: AI for Sustainable Materials, White House Office of Science and Technology Policy, 2024. Available online at: <u>ai.gov/aspirations/</u>

<sup>&</sup>lt;sup>d</sup> National Strategy on Microelectronics Research, A Report by the Subcommittee on Microelectronics Leadership, March 2024. Available online at <u>https://www.whitehouse.gov/wp-content/uploads/2024/03/National-Strategy-on-Microelectronics-Research-March-2024.pdf</u>

(4) Build an exceptional workforce of university graduates and faculty with AI/AE R&D expertise.

The anticipated program outcomes, if successful, should prove relevant and translatable to the NSTC, the CHIPS Manufacturing USA Institute, and other CHIPS programs.

## **1.2 DEFINITIONS**

For purposes of this NOFO, the terms listed below shall have the following meanings:

- (1) **Applied Research** "Original investigation undertaken in order to acquire new knowledge. Applied research is, however, directed primarily towards a specific practical aim or objective."<sup>1</sup>

- (2) **AI-enabled autonomous experimentation** (**AI/AE**) The combination of automated (robotic) hardware for materials synthesis and characterization, AI-powered software and models, and data acquisition, analysis, computational resources, and storage hardware that plan, execute, and evaluate experiments in autonomous closed loops to achieve accelerated research objectives supplied by human researchers.<sup>2</sup>

- (3) **Basic Research** "Experimental or theoretical work undertaken primarily to acquire new knowledge of the underlying foundations of phenomena and observable facts. Basic research may include activities with broad or general applications in mind, such as the study of how plant genomes change, but should exclude research directed towards a specific application or requirement, such as the optimization of the genome of a specific crop species."<sup>3</sup>

- (4) Digital Twin A set of virtual information constructs that mimics the structure, context, and behavior of a natural, engineered, or social system (or system-of-systems). Typically, a digital twin can be dynamically updated with data from its physical twin, has a predictive capability, and informs decisions that realize value.<sup>4</sup>

- (5) Emerging Research Institution or ERI An institution of higher education with an established undergraduate or graduate program that conducts less than \$50,000,000 per year in Federal research expenditures.<sup>5</sup> The Department of Energy maintains an online list of Institution Designations, including ERIs.

- (6) **Materials Digital Twin** Either (i) a model of the performance of material in response to changes in its environment, or (ii) a model of the synthesis of a material, and its response to changes in synthesis control variables.

- (7) **Milestones** Actions or events marking a significant change or stage in developments in a project.

- (8) **Phase-specific Target** Derived from applicant-specified SMART Milestones, phasespecific targets inform go/revise/no-go points for the transition from one project phase to the next. Phase-specific targets may address measurable progress toward either Cooptimization Targets, Programmatic Targets, or both.

- (9) Project All activities funded under a single award made under this NOFO, including but not limited to all planning and management; basic and applied research; the development and production of manufactured materials and devices, systems, equipment, tools, and software, as appropriate to the funded work; preparation for

commercial viability and domestic production of funded innovations; and education and workforce development activities.

- (10) Project Team Any funded entity (the applicant and any proposed subrecipients), as well as unfunded collaborators planned for inclusion in a single proposal under this NOFO.

- (11) **Recipient** The entity that receives an award directly from a Federal awarding agency to carry out an activity under a financial assistance program.

- (12) Research Outputs The results of research funded under this NOFO, including but not limited to data, models, materials, and processes, such as materials property datasets; predictive algorithms; physically manufactured prototype materials; materials digital twins; and manufacturing sustainability design guidelines and frameworks.

- (13) **Semiconductor** An integrated electronic device or system, most commonly manufactured using materials such as, but not limited to, silicon, silicon carbide, or III-V compounds, and processes such as, but not limited to, lithography, deposition, and etching. Such devices and systems include but are not limited to analog and digital electronics, power electronics, and photonics, for memory, processing, sensing, actuation, and communications applications.

- (14) **Semiconductor manufacturing** All activities encompassed by the semiconductor fabrication, advanced packaging, assembly, and test processes, including but not limited to wafer manufacturing.

- (15) **Semiconductor materials** The broad class of materials contained in semiconductor devices and systems (see "semiconductor" definition) as the result of semiconductor manufacturing (which includes packaging), including materials used in semiconductor manufacturing that do not remain in the final product.

- (16) **SMART** A framework for writing objectives that are Specific, Measurable, Achievable, Relevant, and Time-Bound and provide the details for how an organization will achieve an objective.

- (17) **Subrecipient** An entity that is eligible to receive a subaward from a Recipient to carry out activities under an award made under this NOFO, such as research and development activities, education and workforce efforts, and other integral project activities. Vendors selling goods or services in the ordinary course of business are not considered subrecipients for purposes of this NOFO.

- (18) Sustainability / Sustainable The ability to meet the needs of the present without compromising the ability of future generations to meet their own needs. Sustainability has three primary goals: (1) protecting the environment, (2) protecting human health and safety of individuals and communities, and (3) promoting economic prosperity and economic objectives.<sup>6</sup>

# **1.3 BACKGROUND**

In its 2023 Microelectronics and Advanced Packaging Technologies Roadmap, the Semiconductor Research Corporation reported on the demand for innovative, sustainable semiconductor materials and chemistries for current and next generation semiconductors and semiconductor manufacturing. The Roadmap noted that "tools encompassing co-optimization of performance metrics and environmental, health, and safety metrics will help accelerate the discovery of more sustainable materials and chemicals without compromising the performance of the product."<sup>7</sup> Other industry reports, including reports published by the Semiconductor PFAS<sup>e</sup> Consortium, recognize the need for innovation in sustainable materials.<sup>8</sup> These include identifying safer alternatives to existing semiconductor manufacturing materials to developing more effective abatement technologies that prevent the release of chemicals that are harmful to the environment and human health.<sup>9</sup> As the United States and other nations invest in semiconductor manufacturing, these reports reflect a need for manufacturing and its resulting products to demonstrate both high performance and sustainability. While AI/AE provides an opportunity to address these dual objectives, the industry must nonetheless tackle co-existing challenges:

- (1) economic pressure to address sustainability;

- (2) difficulty optimizing across sustainability and performance metrics at the accelerated timelines necessary for impact and competitive edge; and

- (3) the limited AI/AE infrastructure and workforce.

# **1.3.1** Challenge: Economic Pressure

Semiconductor manufacturing requires significant amounts of both water and energy, while using chemicals considered harmful to human health, if released. Examples are as follows:

- The average chip fabrication plant uses 10 million gallons of ultrapure water every day<sup>10,</sup> <sup>11</sup>, the equivalent of 33,000 U.S. homes' consumption;<sup>12</sup>

- Depending on the plant, electricity consumption represents between 5% and 30% of its operating costs, totaling \$20-\$30 million per year. A typical semiconductor plant uses as much energy in a year as about 50,000 homes;<sup>13</sup> and

- In 2022, the electronics manufacturing industry was responsible for 5 million metric tons of CO<sub>2</sub>-equivalent emissions from fluorinated gases.<sup>14</sup>

Given the environmental impact of the semiconductor fabrication process, regulators, manufacturers, and customers have sought more sustainable practices and solutions, including to reduce manufacturing and operating costs as well as litigation and supply chain risks. For instance,

- Prominent semiconductor companies have targeted water reuse/restore/recycle of up to 75% or reductions in water usage reductions by up to 33%;<sup>15</sup>

- At least three manufacturers have announced significant energy consumption reduction, including targets for energy per unit produced, as well significant GHG reduction targets;<sup>16,17,18</sup> and

- One major PFAS supplier is planning to exit the market due to shifting liability.<sup>19</sup> Another PFAS supplier has pledged to phase out certain PFAS related products and processes.<sup>20</sup> Regulatory concerns have raised supply chain risks, with no known alternatives currently existing for many PFAS-containing materials used in the semiconductor industry.<sup>21</sup>

<sup>&</sup>lt;sup>e</sup> Perfluoroalkyl and polyfluoroalkyl substances.

When considering the full product lifecycle, semiconductor products prove even more energyintensive with high environmental impacts. For instance, U.S. data centers comprise roughly 2% of total U.S. electricity usage, according to the Department of Energy.<sup>22</sup>

#### 1.3.2 Challenge: Materials Co-optimization and Time to Deployment

Traditional methods for discovery and deployment of new semiconductor materials—with a focus on improving semiconductor performance while decreasing power usage, physical area, and cost—can require years, even decades, of research, development, testing and validation before deployment.<sup>23</sup> Material characterization experiments, which validate and inform models, are time and labor intensive and often the rate-limiting step in a material validation campaign. Moreover, a lack of validating experiments limits current models of materials design. Including materials sustainability will likely increase these challenges; limit the material candidate pool due to some candidates' toxicity, effects on human health, and environmental impact; and increase the time required for materials discovery and validation. By way of example, when considering the potential for PFAS replacements to impact multiple parts of the precisely-calibrated semiconductor supply chain, the Semiconductor Industry Association (SIA) concluded that timelines for adoption of non-PFAS materials adoption can range from—

- 3 to 4 years, if there is an existing non-PFAS alternative available that can be demonstrated to provide adequate performance for a specific application;

- 3 to 15 years, where existing non-PFAS alternative may be viable but require tooling and/or process changes; and

- Up to 25 years for new chemicals or the development of alternative approaches to manufacturing devices.<sup>24</sup>

#### 1.3.3 Challenge: Limited Research Workforce

In its recent workshop report on AI/AE, an Interagency Working Group of the Materials Genome Initiative (MGI) found an essential role for researchers in "supporting industrial development and aligning fundamental research with broader industry goals, such as carbon neutrality and manufacturability."<sup>25</sup> The Working Group's report further highlighted a demand for graduates trained in autonomous experimentation and materials R&D, with "the combination of AI/ML coding skills and the specific specialization in their respective materials field."<sup>26</sup>

However, the same report estimated that the United States had few institutions ready to conduct fully autonomous AI/AE research in electronics and photonics materials, much less research relevant to semiconductor materials sustainability. This presents a challenge for acquiring the needed research staff, particularly given SIA's projection of 27,300 semiconductor industry engineering roles remaining unfilled due to an insufficient number of graduates in relevant technical fields. These include 9,900 bachelor's, 12,300 master's, and 5,100 PhD-level graduates, in addition to 13,400 computer scientists.<sup>27</sup> A similar assessment by the Department of Commerce Bureau of Industry and Security indicates that the expansion of the semiconductor workforce will require an estimated 54,000 new jobs requiring four-year degrees and 16,000 new jobs not requiring a four-year degree.<sup>28</sup> Given these considerations, the MGI Working Group

specifically identified building the workforce, particularly the U.S. citizen workforce, as a key area for action.

# 1.3.4 Opportunity: AI/AE

Through efforts such as the MGI, the United States has made significant investments into discovering new materials for a range of industries and applications. Recent technological advances, including the rapid improvements in artificial intelligence, suggest an opportunity to more efficiently explore the real-world properties of these and other materials. For instance—

- A major U.S. company leveraged AI/AE to analyze 6,000 data sources to generate 3,000 replacement candidates for potentially toxic semiconductor materials, demonstrating a 100-fold reduction in candidates tested compared to a human toxicologist;<sup>29</sup>

- The Defense Advanced Research Agency (DARPA) funded a multi-location self-driving lab to identify 21 promising materials from a set of 150k+ candidates over two months;<sup>30</sup> and

- A U.S. Department of Energy (DOE) National Lab used AI/AE to synthesize 41 of 58 target compounds over 17 days.<sup>31</sup>

As demonstrated by the efforts described above, AI/AE has a significant advantage over traditional materials R&D methods in allowing researchers to rapidly explore a vast set of design and manufacturing parameters and develop models for their optimization. With direct and continuous contribution from industry on material properties, process requirements, reliability and compatibility, supply chain and cost, and/or lifecycle analysis for sustainability, AI/AE opens a much richer parameter space for co-optimization and should accelerate the time from design to production.

# 1.3.5 Opportunity: Emerging Research Institutions

Multiple Federal laws and policies direct NIST to address shortages in the semiconductor workforce and to increase participation in semiconductor R&D, including by "establishing a dynamic, collaborative network for microelectronics research", "[supporting] a broad range of stakeholders and communities", and "[investing in] workforce development, basic and translational research, and related infrastructure."<sup>f</sup> Emerging Research Institutions provide a unique opportunity to meet this directive while addressing the lack of researchers participating in AI/AE. Per a 2009 National Academies workshop report on ERIs, providing research experiences to students can help increase student retention and employment in the related field, increase the likelihood that students seek graduate education, and improve the participation of underrepresented groups.<sup>32</sup> However, while ERIs serve the majority of students in STEM fields, they receive only 10% of Federal funding for R&D in science and engineering.<sup>33</sup> Increasing ERI research capacity therefore represents an available resource for addressing limitations not only in the amount of experimental data available for AI/AE, but also in the AI/AE and broader semiconductor workforce. Given that it is a relatively new field, one that generally involves the transfer of digital products, and can support distributed research models, AI/AE may be uniquely

<sup>&</sup>lt;sup>f</sup> Executive Order 14080—Implementation of the CHIPS Act of 2022 16

suited to partnerships between ERIs and leading institutions, with ERIs helping to provide both the data and researchers needed to grow the field.

## 1.4 FUNDING OPPORTUNITY DETAILED DESCRIPTION

Consistent with the objectives listed in Section 1.1.2, responsive applications to this NOFO must propose establishing a collaboration among one or more semiconductor industry companies, research universities or national laboratories with demonstrated experience in AI/AE or in related fields, and at least one ERI (or a domestic non-profit or for-profit organization that manage a consortium of ERIs). The National Cooperative Research and Production Act of 1993, as amended (codified at 15 U.S.C. § 4301 et seq.), addresses awardee "joint ventures" (as defined therein) for research and development funded under this award.

Further, consistent with the direction under Executive Order 14080 (Implementation of the CHIPS Act of 2022), CHIPS R&D encourages that proposals include recipients or subrecipients such that awards significantly expand the capabilities of emerging research institutions in partnership with industry, other research universities, and national laboratories.

In order to achieve the objectives of this NOFO, CHIPS encourages and will favorably consider applications that demonstrate strong industry participation in the development of and execution of the funded research. CHIPS R&D further encourages participation by civil society or labor organizations focused on environmental sustainability or human health and safety, where appropriate. Specific project activities are expected to include but not necessarily be limited to:

- (1) establishing the collaboration;

- (2) refining Co-optimization and Programmatic Targets (see Sections 1.4.3 and 1.4.4) relevant to a chosen set of materials classes and applications (see Section 1.4.2);

- (3) conducting basic and applied research guided by the targets;

- (4) training students and faculty; and

- (5) transitioning developed technologies to higher technology readiness levels (TRLs).

#### 1.4.1 Operational Areas

Responsive applications to this NOFO must propose activities, milestones, and deliverables to address the following three Operational Areas (OAs):

- (1) **OA1: Convening, Roadmapping, and Technology Transfer**: Establishing lasting collaborations between stakeholders, refining Co-optimization and Programmatic Targets, and transferring research outputs for further use.

- (2) **OA2: AI/AE Infrastructure and Research**: Establishing AI/AE capabilities, to include infrastructure at ERIs and other research universities or access to such infrastructure, and conducting basic and applied research into early TRL materials and processes that address semiconductor industry needs.

- (3) **OA3: Education and Workforce Development**: Developing and expanding the total number of domestic researchers skilled in AI/AE methods relevant to the semiconductor industry materials and processes.

#### 1.4.2 Materials Classes and Applications

Consistent with the objectives listed in Section 1.1.2, responsive applications to this NOFO must propose focusing project activities on specific material classes and applications relevant to semiconductor manufacturing. Proposals must demonstrate the expected impact on metrics related to both the sustainability of semiconductor manufacturing and to materials, process, or device performance characteristics, which may include device performance, power, area, and cost (PPAC). Proposals may seek to either improve existing materials and processes or enable realization of next-generation materials, processes, or devices.

To support an understanding of the desired approach, Table 2 below provides notional, nonexhaustive examples of materials classes and applications relevant to semiconductor manufacturing. Such examples include:

- **PFAS** Alternatives. Developing and improving the performance of PFAS replacements for use in multiple applications (e.g., photoresists, antireflective coatings, heat transfer fluids, and advanced packaging materials), reducing manufacturing PFAS emissions.

- *Next-Generation Photoresist.* Developing photoresist materials (e.g., resins, solvents, photoactive compounds, etc.), to enable next-generation process nodes while reducing fab energy consumption and emissions.

- *Materials for Improved Device Heat Transfer.* Developing PFAS-free, higher performance thermal interface materials, high conductivity materials, and heat transfer materials for immersion and liquid cooling, to improve the power efficiency of data centers while reducing PFAS emissions throughout the supply chain.

| Tuble 2: 1 (on Exhlustive Eist of 1 (ononal muterials Clusses and Applications |                                      |  |  |  |  |

|--------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| Abatement catalysts                                                            | Memory materials                     |  |  |  |  |

| Adhesives                                                                      | Metals and conductors                |  |  |  |  |

| Atomic Layer Deposition (ALD)                                                  | • PFAS                               |  |  |  |  |

| Antireflective Coatings                                                        | Polymers and resins                  |  |  |  |  |

| Chemical Mechanical Planarization                                              | Photonic materials                   |  |  |  |  |

| (CMP) slurries                                                                 | Photoresists                         |  |  |  |  |

| • Dielectrics and insulators                                                   | • Photoacid generators (PAGs)        |  |  |  |  |

| Dopants                                                                        | • Redistribution Layer films (RDLs)  |  |  |  |  |

| • Epitaxy and deposition gases                                                 | • Solvents                           |  |  |  |  |

| • Etch gases                                                                   | Substrates                           |  |  |  |  |

| • Filters and membranes                                                        | Surfactants                          |  |  |  |  |

| • Heat transfer fluids (HTFs)                                                  | • Thermal Interface Materials (TIMs) |  |  |  |  |

| Interconnects                                                                  | • Underfills                         |  |  |  |  |

| Lubricants                                                                     | • Wet etchants                       |  |  |  |  |

|                                                                                | • 2D materials                       |  |  |  |  |

#### Table 2. Non-Exhaustive List of Notional Materials Classes and Applications

#### 1.4.3 Co-optimization Targets

Responsive applications to this NOFO must propose to pursue—through basic and applied research and the development of analytic models—targeted, industry-relevant materials and processes that co-optimize power- and performance-related materials, process, or device characteristics (see Theme 1 below) and sustainability targets (see Themes 2 - 4 below). Co-optimization Targets that address the environmental impacts of semiconductors over their lifecycle, such as the total power consumed by a device, may be considered within Theme 1. Applications that pursue manufacturing sustainability (Themes 2 - 4) without co-optimizing for Theme 1 will be considered out of scope.

Proposals must address at least one or more of Themes 2, 3, or 4, to target improvements in the sustainability of current or future semiconductor manufacturing techniques. **Proposals that improve device performance without addressing manufacturing sustainability will be considered out of scope.** CHIPS R&D may prioritize applications that credibly address sustainability targets across multiple themes.

#### 1.4.3.1 <u>Theme 1: Materials, Process, or Device Power- and Performance- related</u> <u>Characteristics</u>

Responsive applications to this NOFO must propose Co-optimization Targets based on industryrelevant materials, process, or device power- and performance-related characteristics, which may include PPAC and other related metrics such as yield, economic metrics, and supply chain resiliency metrics. As a notional example, Theme 1 Co-optimization Targets relevant to photoacid generator (PAG) performance and cost criteria include acid strength, acid diffusivity, pattern quality, solubility in casting solvents, manufacturing cost, and processing temperature.<sup>34</sup> More advanced models or digital twins could further consider how changing PAG characteristics might impact downstream process and device performance (including PPAC), via factors such as area scaling or semiconductor design complexity. Conversely, PAG sustainability targets (Themes 2 - 4) may include toxicity and environmental persistence.

CHIPS R&D expects that, in identifying Co-optimization Targets, applications will aim to develop materials and processes that result in similar or improved materials, process, and/or device characteristics compared to currently known materials and processes. If such characteristics do not constitute an improvement over the state of the art or state of the practice, applicants must demonstrate the industry-relevance of the proposal, such as through stakeholder Letters of Commitment/Interest.

#### 1.4.3.2 Theme 2: Emissions and Hazardous Waste

Applications that address Theme 2 must propose Co-optimization Targets that demonstrate improvement related to GHG emissions, use of toxic substances, and generation of hazardous waste from current or future semiconductor manufacturing. Sample targets may include but are not limited to, for instance, the mass or volume of a substance (e.g., GHGs or PFAS) released into the environment per 300mm wafer manufactured. Applicants may further propose to address targets related to the toxicity or human health and safety impact of semiconductor manufacturing-related emissions or hazardous waste.

# 1.4.3.3 <u>Theme 3: Energy Consumption</u>

Applications that address Theme 3 must propose Co-optimization Targets that demonstrate improvement related to the amount of energy consumed by current or future semiconductor manufacturing. Sample target may include but are not limited to, for instance, kilowatt hours (kWh) per 300mm wafer manufactured. Manufacturing energy consumption differs from the amount of power (energy) consumed by a manufactured device, circuit, or system, which would be considered as a potential Theme 1 Co-optimization Target.

#### 1.4.3.4 <u>Theme 4: Water Consumption</u>

Applications that address Theme 4 must propose Co-optimization Targets that demonstrate improvement related to water consumed by current or future semiconductor manufacturing. Targets may include, but are not limited to, targets related to amount of fresh water consumed from public utilities as well as targets related to recycling or reclamation of used process water. Sample targets may include but are not limited to, for instance, gallons of water used per 300mm wafer manufactured.

#### **1.4.4 Programmatic Targets**

Responsive applications to this NOFO must propose to pursue improvements in the domestic capabilities for AI/AE research (Theme 5) and in the research-trained semiconductor workforce (Theme 6). Responsive applications must further propose to pursue the domestic transfer of CHIPS-funded technologies (Theme 7).

#### 1.4.4.1 <u>Theme 5: Research Capacity</u>

Applications must propose Programmatic Targets that demonstrate how CHIPS-funded activities will increase the overall research capacity of the domestic semiconductor innovation ecosystem, particularly as it relates to AI/AE. Sample targets may include but are not limited to, for instance:

- (1) the number of faculty able to substantively engage in relevant research, including after the period of performance;

- (2) the administrative and physical infrastructure (e.g., equipment) available for performing AI/AE research in sustainable semiconductor materials at funded institutions, including through co-investment;

- (3) the long-term availability, both to universities and industry, of physical and digital infrastructure for AI/AE research; and

- (4) the overall research productivity of funded institutions (e.g., publication activity, patent activity, or research expenditures) in semiconductor-related fields, and

- (5) partnerships with entities focused on innovation, entrepreneurship, access to capital, and technology commercialization.

Applications must specify the distribution of increased research capacity between ERIs and non-ERIs. CHIPS R&D will favorably consider applications that demonstrate a substantial increase in research capacity and research leadership at ERIs.

#### 1.4.4.2 Theme 6: Education and Workforce Development

Applications must provide an **Education and Workforce Development (EWD) Plan** with Programmatic Targets that represent improvements in the availability of state-of-the-art (SOTA) research-trained personnel. Sample targets may include but are not limited to, for instance, improvements in:

- (1) the number of undergraduate, masters, or doctoral students provided significant research experiences (e.g., paid research internships and fellowships) and direct mentorship by industry or other private sector partners in semiconductor-relevant AI/AE research;

- (2) the number of relevant industry and other private sector roles within educational institutions (e.g., visiting scientists, adjunct faculty, and research fellows),

- (3) access to semiconductor or AI/AE relevant training at the partner educational institutions; and

- (4) the number of graduating students that enter the domestic semiconductor workforce in manufacturing, design, and R&D.

Applications must specify the distribution of EWD improvements between ERIs and non-ERIs. CHIPS R&D will favorably consider applications that demonstrate substantial EWD improvements at ERIs.

#### 1.4.4.3 <u>Theme 7: Domestic Technology Transfer</u>

Applications must propose Programmatic Targets that demonstrate, with rigor increasing across the award period of performance, the ability for CHIPS-funded research outputs to successfully transfer to the domestic commercial marketplace. CHIPS R&D strongly encourages applicants to work with industry partners when developing these targets and to ensure consistency with the **Commercial Viability and Domestic Production Plan (CVDP)** as discussed in Section 2.6.4 of this NOFO. Sample targets may include but are not limited to, for instance:

- (1) the number and quality of industry partnerships, including through a Research Advisory Board (RAB);

- (2) direct participation of industry in research funded under this award;

- (3) participation of funded institutions in the CHIPS Manufacturing USA Institute;

- (4) patenting and licensing activities, or other evidence indicating the adoption of funded research outputs by domestic partners or by CHIPS-funded programs;

- (5) measures of alignment with industry needs, as demonstrated through technoeconomic analyses, relevant co-investment, or other means; and

- (6) the number and quality of research outputs transitioned to industry for testing or integration into co-optimization models or pilot lines, where appropriate.

Applicants should be aware that the CVDP represents an initial assessment of the commercial viability and domestic production opportunities of potential funded research outputs, with

updates occurring across the award period. Given this NOFO's focus on industry-informed, university-based collaborations, CHIPS R&D anticipates that Phase 1 Theme 7 targets may largely focus on strengthening industry partnerships, conducting technoeconomic analyses, and informing the CVDP. CHIPS R&D expects that awardees will refine more definitive applicant-proposed metrics for technology transfer during Phase 1, for tracking during Phases 2 and 3.

#### 1.4.5 Phases of Work and SMART Milestones

Responsive applications to this NOFO must propose three phases of work, with the first phase ranging from 12 to 18 months and each subsequent phase ranging in length from 12 to 24 months. The total period of performance may not exceed five (5) years.

Responsive applications to this NOFO must further define, for each OA and within each phase, SMART Milestones marking measurable progress towards demonstrating the Co-optimization Targets (Section 1.4.3) and achieving the Programmatic Targets (Section 1.4.4).

In coordination with NIST's Financial Assistance Agreements Management Office (FAAMO), CHIPS R&D may conduct negotiations with applicants deemed meritorious by the evaluation panel and determined by CHIPS R&D to stand a reasonable chance of being funded, in order to (1) refine the proposed milestones (2) define phase-specific targets derived from the proposed milestones, and (3) address other matters as determined by CHIPS R&D. These phase-specific targets will inform go/revise/no-go points for the transition from one project phase to the next.

Upon approval and selection of an application under this NOFO, CHIPS R&D intends to award funding for Phase 1 activities across all Operational Areas, with subsequent phases being considered for funding incrementally. CHIPS R&D retains sole discretion to determine whether a recipient has met the requirements for each Co-optimization Target, Programmatic Target, Phase-specific target, milestone, and deliverable.

Based on the results of CHIPS R&D assessments of research outputs, evaluation of overall progress, availability of funding, and continued alignment with CHIPS R&D priorities, CHIPS R&D, at its sole discretion, will decide at the end of each phase to proceed with the next increment of funding, request a revised plan from the recipient (subject to both the constraints of the approved award scope and budget, and subject to CHIPS R&D approval), or terminate funding for the project.

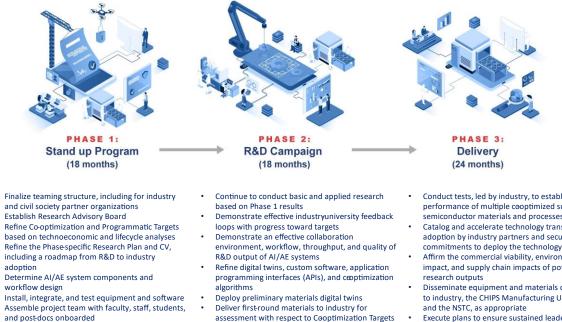

Figure 1 below shows a hypothetical project timeline with three phases of 18 months, 18 months, and 24 months, with corresponding milestones.

- Refine EWD Plan and begin to develop and teach AI/AE curricula at participating universities

- Join CHIPS Manufacturing USA Institute and the NSTC, as appropriate

- and AI/AE system performance

- Update EWD plan and continue to train students and post-docs using relevant AI/AE curricula

- Conduct tests, led by industry, to establish the performance of multiple cooptimized sustainable semiconductor materials and processes

- Catalog and accelerate technology transfer and adoption by industry partners and secure industry commitments to deploy the technology

- Affirm the commercial viability, environmental impact, and supply chain impacts of potential

- Disseminate equipment and materials digital twins to industry, the CHIPS Manufacturing USA Institute,

- Execute plans to ensure sustained leadership, capabilities, and capacity for AI/AE at universities, including ERIs, and in the private sector

- Deliver final reports and best practice at CHIPS R&D

#### 1.4.6 **Project Team Capabilities and Structure**

AI/AE couples automated experimentation (robotically controlled experiments), in situ or inline analysis of experimental results, and the use of artificial intelligence as a decision engine to direct experiments in rapid, closed loops. In responding to this NOFO, CHIPS R&D encourages applicants to consider existing best practices for using artificial intelligence and for AI/AE, including incorporating the major components of an AI/AE system described below. Responsive applications may also consider the role of federated architectures and must include a physical infrastructure and faculty development plan.

#### 1.4.6.1 Major Components of an AI/AE System