## **Connectors, Including RF & Photonics**

### **PM: Christopher Myatt**

### **Disclaimer**

Statements and responses to questions about advanced microelectronics research and development programs in this webinar:

- Are informational, pre-decisional, and preliminary in nature.

- Do not constitute a commitment and are not binding on NIST or the Department of Commerce.

- Are subject in their entirety to any final action by NIST or the Department of Commerce.

Nothing in this presentation is intended to contradict or supersede the requirements published in any future policy documents or Notices of Funding Opportunity.

### **Existing Connectors vs. NAPMP Vision**

Connectors currently limit data communication in and out of the package

| In-Package              | Existing Connectors                              |               |                               |

|-------------------------|--------------------------------------------------|---------------|-------------------------------|

| < 5mm                   | 5 – 25mm                                         | <5m           | <1km                          |

| Die-to-Die Connectors   | On-board                                         | Backplane     | Optical Transceivers          |

| e.g. UCIe<br>• 5Tb/s/mm | <ul><li>PCle 112G XSR</li><li>1Tb/s/mm</li></ul> | • 0.87Tb/s/mm | 800G QSFP-DD<br>• 0.05Tb/s/mm |

NAPMP Vision for high efficiency, high bandwidth, low error rate connectors

| In-Package                                                                         | NAPMP Connectors                                                                             |                                                                                                                                  |                                                                                           |  |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| < 5mm                                                                              | <25mm                                                                                        | <1m                                                                                                                              | <1km                                                                                      |  |

| <b>Chiplet to Chiplet</b><br>Covered under Chiplet NOFO<br>Utilizes Wire abundance | Flexible Wired Con.<br>Sub-assembly to sub-assembly<br>Shoreline BW density<br>• > 10Tb/s/mm | Wired or Wireless Con.<br>Sub-assembly to Sub-assembly<br>Bidirectional Bandwidth =<br>• > 100Tb/s<br>Power Efficiency < 0.1pJ/b | Co-packaged optic Con.<br>Sub-assembly to Sub-assembly<br>Bidirectional BW<br>• > 100Tb/s |  |

### **Three Length Scale Objectives**

| Objective                                           | Length Scale | Key Characteristics                                                                                                                    |

|-----------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Short Range (e.g. Wired)                            | L < 25 mm    | Data rates of > 10 Gb/s/channel & density of 10 Tb/s/mm<br>Power efficiency < 0.1 pJ/bit including all energy for full functionality   |

| Intermediate Range (e.g.<br>RF, Wired, or Photonic) | L < 1 m      | Aggregate data rate > 100 Tb/s bidirectional from package<br>Power efficiency < 0.1 pJ/bit including all energy for full functionality |

| Long Range (e.g. Photonic)                          | L < 1 km     | Aggregate data rate > 100 Tb/s bidirectional from package<br>Power efficiency < 0.1 pJ/bit including all energy for full functionality |

|                                                     |              | Short Range ( <i>L</i> < 25 <i>mm</i> )                                                                                                |

|                                                     | $\prec$      | Intermediate Range ( <i>L</i> < 1 <i>m</i> )                                                                                           |

| Wafer Scale System                                  |              | Long Range ( <i>L &lt; 1 km</i> )                                                                                                      |

|                                                     |              |                                                                                                                                        |

### **Connector Technology, Including Photonics and RF R&D Areas**

#### **RDA Drivers**

Recent years have seen an explosion of progress in high performance computing. Data transmission in these systems requires innovation for high data-rate, low latency, small footprint, error-free, and energy efficient connections.

#### Objectives

- Development of short-range, wired connections to enable high speed connectivity between neighboring packages.

- Development for intermediate range wired, photonic, or wireless connectors between local wafer-scale systems (but not necessarily nearest neighbor).

- Development of long-range connectors capable of connecting wafer-scale systems at a range up to and exceeding the length of a server site, or approximately 1 km

#### **Key Outputs**

- Novel connectors, tools, materials, processes and devices with improved performance

- Standards and metrologies derived from test devices; test and evaluation at proto- and pilot-scale manufacturing

- Provide new connector solutions, including devices, equipment, tools, processes, and process integration, to research projects in other areas of packaging research

#### Out of Scope

- Traditional ball grid array (BGA) or land grid array (LGA) connectors,

- Conventional wire bonding

- Traditional free space optical components

### **Key Technical Metrics: Connectors**

- Technical Metrics are intended to push the state of the art

- Targets are aggressive, but value will be placed on versatility, flexibility, and manufacturability in approach

- Performers can call out specific targets that are out of scope or at risk

- Performers should specify their target FOM and the trade-offs considered for their technology to optimize the overall performance

|                                                                | Objective 1                   | Objective 2                                       | Objective 3                |  |

|----------------------------------------------------------------|-------------------------------|---------------------------------------------------|----------------------------|--|

| Distance                                                       | 5 - 25 mm                     | < 1 m                                             | < 1 km                     |  |

| Bandwidth<br>Req.                                              | 10Gb/s/channel &<br>10Tb/s/mm | >100 Tb/s<br>bidirectional                        | >100 Tb/s<br>bidirectional |  |

| Efficiency                                                     | < 0.1 pJ/b                    |                                                   |                            |  |

| Clock Rate<br><i>OR</i><br>RF Freq.<br><i>OR</i><br>Wavelength | Applicant Defined             | Applicant Defined                                 | Applicant Defined          |  |

|                                                                | N/A                           | 20 – 220 GHz                                      | N/A                        |  |

|                                                                | N/A                           | Align with existing MSA* or provide justification |                            |  |

| Latency                                                        | <2 ns + TOF                   |                                                   |                            |  |

| BER (w/ error correction)                                      | <10 <sup>-12</sup>            |                                                   |                            |  |

|                                                                |                               |                                                   | * e.g. CW-WDA MSA          |  |

| Ontimiza f                                                     | о ГоМ —                       | (BW/shoreline)                                    | * link length              |  |

| Opumize to                                                     | or: s-FoM = -                 | Efficiency * connector area * latency             |                            |  |

Jangam, Iyer, 10.1109/TCPMT.2020.3022760

### **Specifications**

#### Applicants must call out their targets for the following parameters

| Bandwidth/shoreline (Gb/s/mm)              | The effective data rate assuming all signal escapes are from the edge of the sub-assembly                                                                                                          |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bandwidth/area (Gb/s/mm²)                  | The effective data rate accounting for all the area used by the connector                                                                                                                          |

| Total chiplet area (mm²)                   | Total Area of the chiplet including any elements needed to enable full functionality                                                                                                               |

| Link length (mm)                           | The length in mm between the transmitter and receiver                                                                                                                                              |

| Energy efficiency (pJ/bit)                 | The amortized energy per bit transmitted, including source (laser), modulation, SerDes, error correction, etc.                                                                                     |

| Clock rate <i>OR</i><br>RF freq. <i>OR</i> | Proposer specified. Explain adherence to an MSA or other interoperability specifications should be                                                                                                 |

| Wavelength                                 | stated                                                                                                                                                                                             |

| Wavelength<br>Latency (ns)                 | Total time for the electrical data being transmitted to be prepared, transmitted and received, in usable error-free electrical form, including time of flight (TOF) which can be stated separately |

### **Key Outputs**

#### **3-5 Year Outputs**

- New materials, designs, documentation, processes, and tools to prototype and demonstrate manufacturability.

- Innovative approaches for both flexible wired and wireless connections relying on RF/mm-wave and/or optical approaches

- New measurement methods for connector chiplets and substrate/sub-assembly features, to improve materials, models, designs, processes and tools for connector solutions and data transfer management.

- Connector modeling capabilities for complex advanced packaging flows; Validated connector models and connector assembly reliability data that are aligned with new design tools developed under the NAPMP Co-Design/Electronic Design Automation RDA and other semiconductor R&D initiatives.

- The assembly technologies and processes will involve development of tooling for bonding.

#### **10 Year Outputs**

- Scale down and scale out connectors are no longer gating factors limiting advanced packaging for all data rate transfer distances.

- Devices assembled with advanced packaging connectors operate reliably at higher power performance and higher energy efficiency.

- Chiplets and connector substrate features developed under this award are readily available in the chiplets ecosystem.

- Extreme interconnect density needs of next-generation packaging will drive fine pitches (< 10 µm pitch) and line/space (< 1 µm L/S) circuitry.</li>

**Goal:** Drive innovation and adoption for high data-rate, low latency, small footprint, error-free, and energy efficient connections between packaged sub-assemblies.

### **Key Deliverables**

|                                     |                                         | Year 1<br>1Q 2Q 3Q 4Q                                  | Year 2<br>5Q 6Q 7Q 8Q                                         | Year 3 Year 3   9Q 10Q 11Q 12Q 13Q 14Q     | ear 4 Year 5<br>15Q 16Q 17Q 18Q 19Q 20Q                 |

|-------------------------------------|-----------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|

| Example Deliverable<br>Plan for TA3 |                                         | Phase 1: Develop<br>preliminary connector<br>solutions | <u>Phase 2:</u> Develop<br>prototypes of initial<br>solutions | Phase 3: Refinement of connector solutions | Phase 4: Transfer of the leading solutions to the NAPPF |

|                                     | Faster / More accurate<br>modulators    |                                                        |                                                               |                                            |                                                         |

| PIC                                 | Consolidate EIC / PIC                   | Layout/                                                |                                                               |                                            |                                                         |

|                                     | Smaller footprint,<br>denser shoreline  | Determine<br>Specs                                     | Prototypes                                                    |                                            | Transfer to NAPPF                                       |

|                                     | Athermal design                         |                                                        |                                                               | Process/<br>Quality Optimization           |                                                         |

| Connector<br>/Coupling              | Microlens vs. Evanescent                | Decision on Method                                     |                                                               |                                            |                                                         |

|                                     | Fiber attach:<br>Vertical or horizontal | Determine Specs                                        | Work w/ Tool Vendors                                          |                                            |                                                         |

|                                     | Method of wafer testing                 | Decision on Method                                     | Work w/ Tool Vendors                                          |                                            |                                                         |

| Operation                           | Energy budget per bit                   | Model/Estimate                                         | Prelim. Measurements                                          | Final Design Results                       | Verify results in NAPPF Parts                           |

|                                     | Error correction                        | Design Circuit / Sware                                 | Software V&V                                                  | Test in Device                             | Verify results in NAPPF Parts                           |

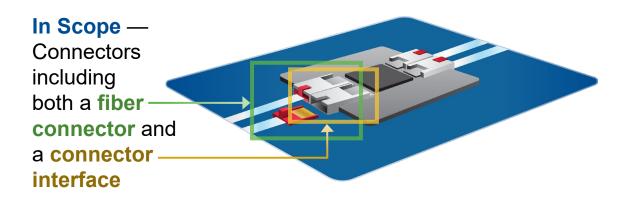

### In Scope/Out of Scope

#### In Scope

- Chiplet sub-assembly to substrate connectors and connection techniques, such as:

- Automated, low loss, reliable fiber attachment approaches such as high fiber count fiber array units (FAUs) that may contain polarization maintaining fibers

- Flip-chip optical connections, including evanescent coupling, between substrate waveguides and transceiver chiplets

#### **Out of Scope**

- Traditional ball grid array (BGA) or land grid array (LGA) connectors

- Conventional wire bonding

- Traditional free space optical components

#### Out of Scope —

Connectors utilizing wire bonds from substrate to package

#### Out of Scope —

Traditional free space optical components such as those used in some pluggable transceivers

#### **Collaboration with Other R&D Areas** Minimize thermal burden Tools must offer process capabilities to process Avoid localized hotspots connector technology Process flow needs to be compatible with other • Enable reliability in extreme conditions process flows (i.e. post fiber attach reflow...) • Chiplet to Advanced models power deliv substrate optical • Leverage to connectors (Photonics & RF) coupling accelerate design In-substrate optical routing • Match fine scale o-design/ & bonding ctronic chiplets ecosystem National Advanced Packaging Piloting Facility **Transition Connector** • Optimize for chiplet technology and interconnect technology processes to NAPPF Chiplet-like connector interface

### **Program Structure**

CHIPS

- Multiple awards varying in scope and funding are expected:

- Up to approximately \$250,000,000 anticipated for funding multiple awards in amounts ranging from a minimum of approximately \$10,000,000 up to a maximum of approximately \$100,000,000

- Multi-disciplinary, multi-organization project teams are strongly encouraged

- Applicants must propose a detailed project plan for achieving Project-Level Technical Targets

- Projects should be divided into 4 phases over a period of performance of 5 years:

- Phase 1 (12 months)

- Phase 2 (12 months)

- Phase 3 (18 months)

- Phase 4 (18 months)

- While cost share is not required, CHIPS R&D will give preference to applications that demonstrate credible cost share commitments

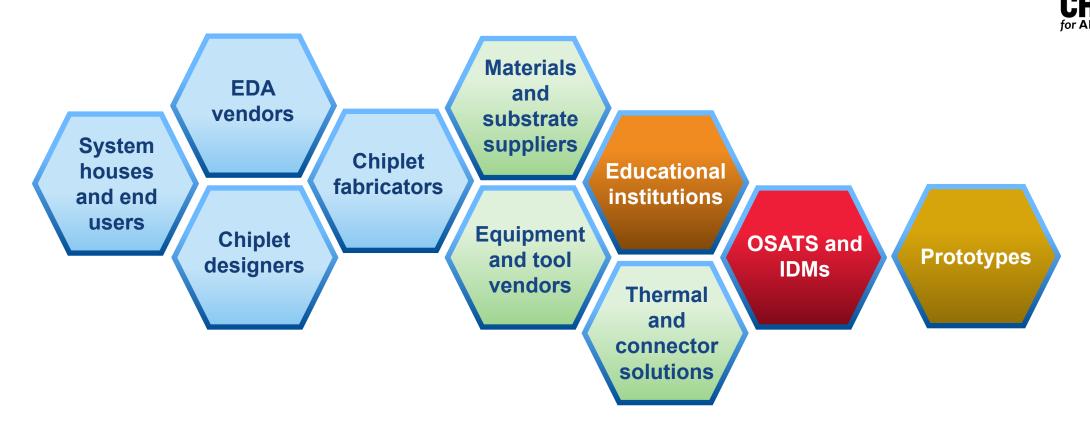

## **Collaboration is Critical for Success**

Successful execution will require collaboration between proposers and each R&D Area. Proposers must clearly understand the ideas presented in each R&D Area. We encourage you to begin identifying your individual contributions to the ecosystem as well as partners who can help accomplish the vision and goals of the NAPMP.

### **Next Steps**

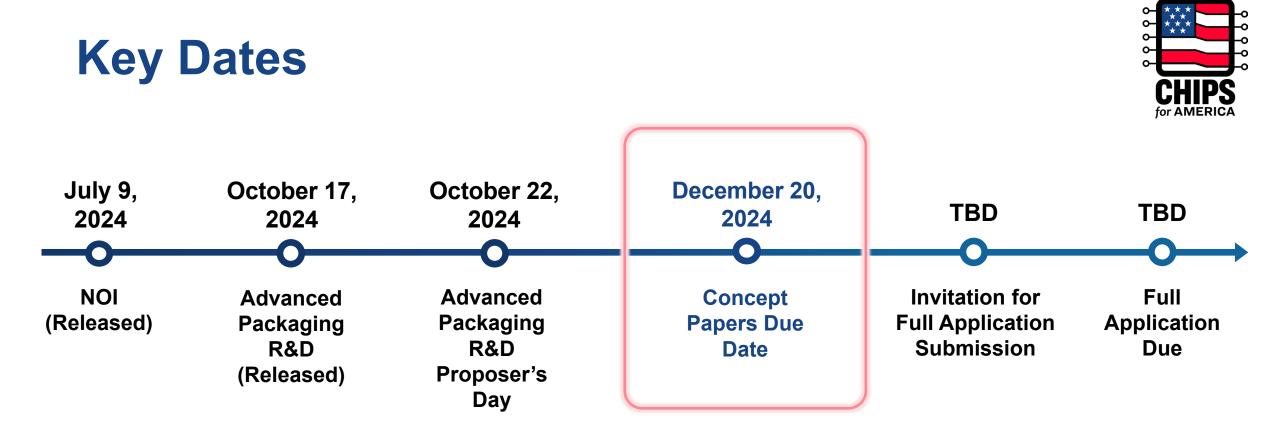

- NOFO 2: Concept papers due 12/16

- Visit <u>CHIPS.gov</u> for resources, including:

- Upcoming R&D Area Webinars

- FAQs

- Funding opportunities and NOFO updates

- Join our mailing list

- Contact us

- <u>askchips@chips.gov</u> general inquiries

- <u>apply@chips.gov</u> application-related inquiries

# Thank you for attending

Visit CHIPS.gov for future updates and additional information