PM: David A. LaVan

October 22, 2024

### **Disclaimer**

Statements and responses to questions about advanced microelectronics research and development programs in this webinar:

- Are informational, pre-decisional, and preliminary in nature.

- Do not constitute a commitment and are not binding on NIST or the Department of Commerce.

- Are subject in their entirety to any final action by NIST or the Department of Commerce.

Nothing in this presentation is intended to contradict or supersede the requirements published in any future policy documents or Notices of Funding Opportunity.

- Address power delivery, power efficiency, and thermal management challenges for advanced packaging.

- Create test devices, utility chiplets and improved models to develop and refine thermal and power solutions for the advanced packaging ecosystem.

- Ensure that thermal dissipation and power delivery will no longer be gating factors that limit advanced packaging.

### **Critical Objectives**

- Power Delivery and Management

- Thermal Management

- Higher Fidelity Power and Thermal Models

- Integrated Power and Thermal Management

### Key Outputs

- Test devices and utility chiplets

- Multi-use solutions

- Standards, metrologies and data derived from test devices

- Test and evaluation at prototype- and pilotscale manufacturing

- Proven equipment, tools, processes, materials, models and devices with improved performance available for the CHIPS ecosystem

#### Out of Scope

- Single-use thermal and power solutions

- Conventional air-cooling approaches

- Discrete packaged wide bandgap devices

- Discrete passives

- Development of batteries

### Drivers

- Innovate to deliver power efficiently, locally, and dynamically

- Produce less waste heat

- Support integration with emerging technologies, such as photonics and connectors

- Spread and tolerate heat more effectively

- Improve heat removal and management strategies

- Improve models to accelerate design and validation

- Multi-use solutions that benefit many applications and the Chiplet ecosystem

### Outcomes

Enable advanced packaging for reliable operation at higher power densities and improved energy efficiencies

### **Four Critical Objectives**

| Objective                                     | High Performance                                                                                                                                                                       | Low-Power                                                                                   |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| 1. Power Delivery and<br>Management           | Power delivery at high density and high efficiency for 3DHI devices                                                                                                                    | Design optimization, energy<br>efficiency, and integrated energy<br>harvesting technologies |  |

| 2. Thermal Management                         | Thermal solutions compatible with advanced<br>substrates, 3DHI, and other advanced packaging<br>design aspects to reduce hotspots, maintain<br>thermal targets, and enable reliability | Compact and lightweight thermal solutions                                                   |  |

| 3. Thermal and Power<br>Models                | Validated, higher fidelity thermal and power models that accurately predict power and thermal distributions across chiplet stacks and accelerate advanced system design and evaluation |                                                                                             |  |

| 4. Integrated Thermal and<br>Power Management | Achieve efficiency and power density goals with integrated designs that couple power delivery and thermal management strategies, for use with fine-pitch, bonded stacks of chiplets    |                                                                                             |  |

### Proposals for the Thermal and Power Delivery R&D Area must address one or more of the four objectives

- Novel equipment, tools, materials, processes, devices, data and models that demonstrate improved performance for Thermal and Power solutions.

- Utilization of test devices and chiplets to demonstrate performance in 3DHI stacks with a path to scale.

- Standards, metrologies and data derived from test devices.

- Test and evaluation at prototype- and pilot-scale manufacturing.

- Proven processes, materials, models and devices with improved performance available for the CHIPS ecosystem:

- Power delivery and thermal management chiplets to support the chiplet ecosystem

- Thermal solutions and power solutions made available to other CHIPS R&D projects

- Thermal solutions that do not constrain connectivity and are compatible with advanced substrates and 3DHI

### **Key Deliverables**

| Year 1                                                         | Year 2                                  | Year 3                                                             | Year 4                  | Year 5                                           |  |

|----------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------|-------------------------|--------------------------------------------------|--|

| 1Q 2Q 3Q 4Q                                                    | <mark>5Q 6Q 7Q 8</mark> Q               | 9Q 10Q 11Q 12Q                                                     | <b>13Q 14Q 15Q 16</b> Q | 17Q 18Q 19Q 20Q                                  |  |

| Phase 1: Set-up<br>facilities, demonstrate<br>utility chiplets | Phase 2:<br>Demonstrate test<br>devices | Phase 3: Refine tecl<br>approach and begin tra<br>other facilities | nsition to Phase 4:     | Phase 4: Transition solutions to NAPPF           |  |

| Utility chiplets                                               | Test devices                            | Demonstration devices                                              | Scaling to pi           | lot-level production                             |  |

| Thermal and power demonstration devices                        | Thermal and power solutions samples     | Thermal and power solution                                         |                         | ermal and power<br>use in other research<br>reas |  |

- Thermal and power solutions that are modular, reusable, and useful for multiple applications within the chiplet ecosystem

- Thermal management

- Vertical heat extraction

- Local heat spreading

- Embedded cooling

- Advanced methods for active and passive cooling of 3DHI devices to reliably operate at higher power density

- Wide bandgap chiplets using 3DHI for power delivery

- Advanced models, materials, and architectures to achieve specific thermal goals such as lowresistance thermal interfaces

- On chiplet embedded structures, passives, 3D stacks, and films for power delivery and thermal management

### **Out of Scope**

Single-use thermal and power solutions

Why? Modular / multi-use solutions that will most benefit the chiplet ecosystem

Conventional air-cooling approaches

Why? To drive improvements in power density, efficiency, size, weight and connectivity

Discrete packaged devices and Discrete passives

**Why?** Advanced Packaging is about scale down and scale out - greater connectivity and many heterogenous chiplets integrated together within a package

Development of batteries

**Why?** Improvements in energy harvesting with possible integrated storage would benefit low-power and sensor applications, not stand-alone batteries

### **Program Structure**

- Multiple awards varying in scope and funding are expected

- Up to approximately \$250,000,000 anticipated for funding multiple awards in amounts ranging from a minimum of approximately \$10,000,000 up to a maximum of approximately \$50,000,000

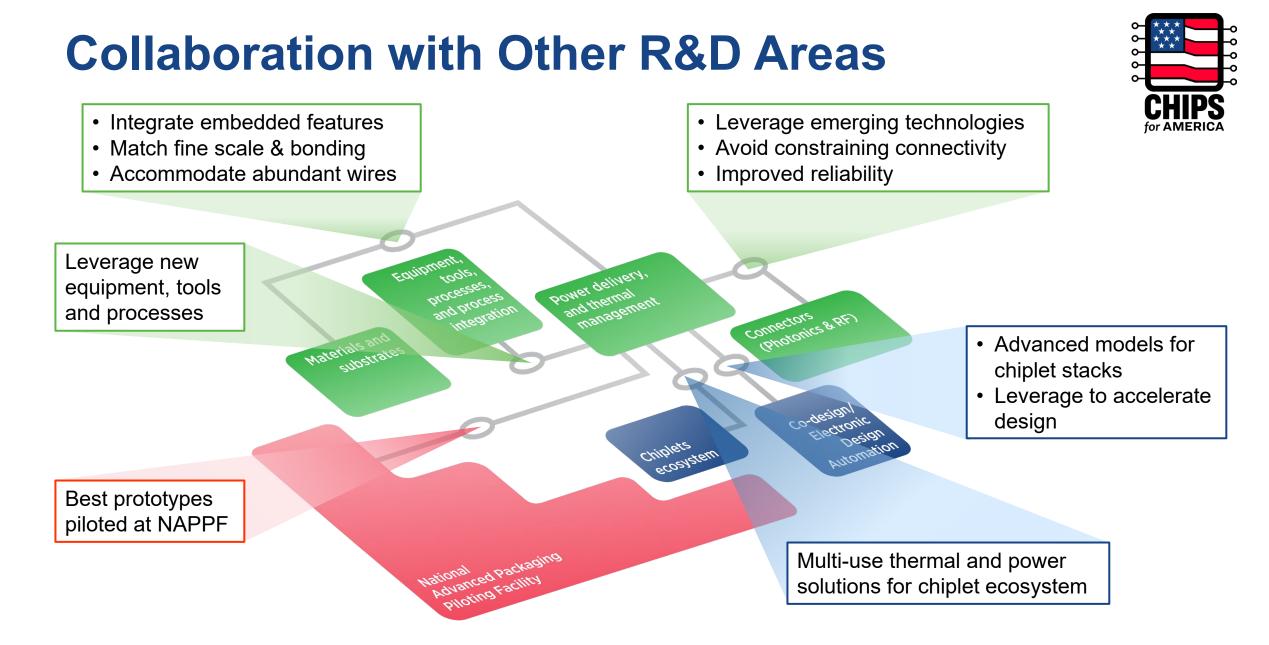

- Multi-disciplinary, multi-organization project teams are strongly encouraged

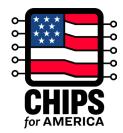

- Project teams should expect to collaborate with other R&D Areas

- Applicants must propose a detailed project plan for achieving Project-Level Technical Targets

- Projects should be divided into 4 phases over a period of performance of 5 years

- Phase 1 (12 months)

- Phase 2 (12 months)

- Phase 3 (18 months)

- Phase 4 (18 months)

- While cost share is not be required, CHIPS R&D will give preference to applications that demonstrate credible cost share commitments. Cost share generally consists of labor, materials, equipment, software, facilities costs, and other investments directly related to the project.

# **Collaboration is Critical for Success**

Successful execution will require collaboration between proposers and each R&D Area. Proposers must clearly understand the ideas presented in each R&D Area. We encourage you to begin identifying your individual contributions to the ecosystem as well as partners who can help accomplish the vision and goals of the NAPMP.

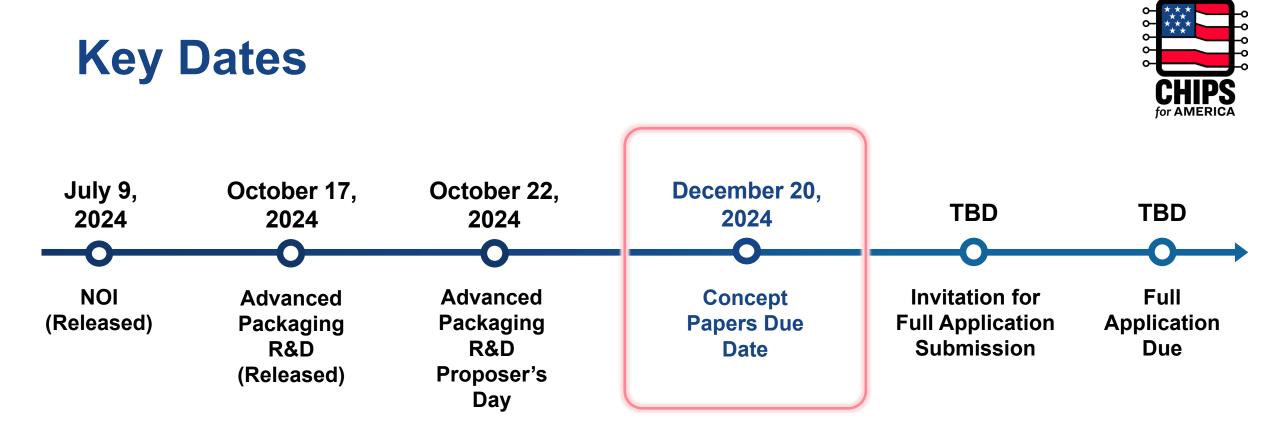

### **Next Steps**

- NOFO 2: Concept papers due 12/16

- Visit <u>CHIPS.gov</u> for resources, including:

- Upcoming R&D Area Webinars

- FAQs

- Funding opportunities and NOFO updates

- Join our mailing list

- Contact us

- <u>askchips@chips.gov</u> general inquiries

- <u>apply@chips.gov</u> application-related inquiries

# Thank you for attending

Visit CHIPS.gov for future updates and additional information